Abstract

In this paper, the nanotube electrostatic plasma-based tunnel field-effect transistor (EP-NTTFET) has been proposed. The use of external bias on the side contacts of the source/drain region helps in the induction of charge carriers even with the use of the polysilicon electrode. The analog parameters are studied such as OFF-current, ON-current, ION/IOFF, sub-threshold slope, threshold voltage, transconductance, TGF, cut-off frequency and DIBL with channel length (LC), Nanotube radius (TSi) and Source voltage (VS) variation. The channel length (LC) varies from 10 to 50 nm, OFF-current varies from 3.79 × 10–13 A/um to 6.79 × 10–19 A/um, sub-threshold slope improves from 36.88 mV/decade to 9.6 mV/decade and ION/IOFF current ration improves from the order of 107 to 1013. The nanotube radius (TSi) varies from 3.5 nm to 12 nm, so ON-current varies from 2.6 × 10–5 A/um to 4.78 × 10–5 A/um, OFF-current increases and sub-threshold slope increases from 18.28 mV/decade to 26.9 mV/decade. The source voltage (VS) varies from – 0.2 V to – 1.2 V, so ON-current varies from 7.88 × 10–6 A/um to 3 × 10–5 A/um, OFF-current increases from 6.5 × 10–19 A/um to 2.25 × 10–15 A/um, sub-threshold slope improves from 24.84 mV/decade to 20.83 mV/decade and threshold voltage decreases from 0.36 V to 0.25 V. To reduce the thermal budget with simple fabrication steps and lower random dopant fluctuations (RDFs) electrostatics plasma-based nanotube TFET is used. The proposed device EP-NTTFET provides higher ON current, higher ION/IOFF current ratio, better sub-threshold slope, and lower threshold voltage.

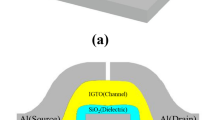

source to drain contact. c 2-D structure of EP-NTTFET across the cutling AA’. d Colour indication of different materials used in Fig. 1

Similar content being viewed by others

References

R.R. Schaller, Moore’s law: Past, present and future. IEEE Spectr 34(6), 52–59 (1997). https://doi.org/10.1109/6.591665

R.H. Yan, A. Ourmazd, K.F. Lee, Scaling the Si MOSFET: From bulk to SOI to bulk. IEEE Trans Electron Devices 39(7), 1704–1710 (1992). https://doi.org/10.1109/16.141237

Y. Choi, B.G. Park, J.D. Lee, T.-J.K. Liu, Tunneling field-effect transistors (TFETs) with subthreshold swing (SS) less than 60 mV/dec. IEEE Electron Device Lett 28(8), 743–745 (2007). https://doi.org/10.1109/LED.2007.901273

Krishnamohan T, Kim D, Raghunathan S, Saraswat K (2008) “Double-gate strained-Ge heterostructure tunneling FET (TFET) with record high drive currents and 60 mV/dec subthreshold slope,” in Proc. IEEE Int Electron Devices Meet 10.1109/IEDM.2008.4796839

M.K. Mamidala, R. Vishnoi, P. Pandey, Tunnel field-effect transistors (TFET): Modelling and Simulation (Wiley, West Sussex, 2016)

Sahoo S, Dash S, Mishra GP (2019) “Work-function modulated hetero gate charge plasma TFET to enhance the device performance,” 2019 Devices for Integrated Circuit (DevIC), Kalyani, India. 461–464. 10.1109/DEVIC.2019.8783943

N. Kumar, A. Raman, Design and Investigation of Charge-Plasma-Based Work Function Engineered Dual-Metal-Heterogeneous Gate Si-Si0.55Ge0.45 GAA-Cylindrical NWTFET for Ambipolar Analysis. IEEE Trans. Electron Devices 66(3), 1468–1474 (2019). https://doi.org/10.1109/TED.2019.2893224

H. Agarwal et al., Proposal for Capacitance Matching in Negative Capacitance Field-Effect Transistors. IEEE Electron Device Lett. 40(3), 463–466 (2019). https://doi.org/10.1109/LED.2019.2891540

A.K. Gupta, A. Raman, N. Kumar, Design and Investigation of a Novel Charge Plasma-Based Core-Shell Ring-TFET: Analog and Linearity Analysis. IEEE Trans. Electron Devices 66(8), 3506–3512 (2019). https://doi.org/10.1109/TED.2019.2924809

S. Sahay, M.J. Kumar, ‘A novel gate-stack-engineered nanowire FET for scaling to the sub-10-nm regime’. IEEE Trans. Electron Devices 63(12), 5055–5059 (2016). https://doi.org/10.1109/TED.2016.2617383

J.P. Colinge, C.W. Lee, A. Afzalian, N.D. Akhavan, R. Yan, I. Ferain, P. Razavi, B. O’Neill, A. Blake, M. White, A.M. Kelleher, B. McCarthy, R. Murphy, Nanowire transistors without junctions. Nat. Nanotechnol. 5(3), 225–229 (2010). https://doi.org/10.1038/nnan0.2010.15

N. Kumar, U. Mushtaq, S.I. Amin, S. Anand, Design and performance analysis of dual-gate all around core-shell nanotube TFET. Superlattices Microstructures 125, 356–364 (2019). https://doi.org/10.1016/j.spmi.2018.09.012

S. Sahay, M.J. Kumar, Comprehensive Analysis of Gate-Induced Drain Leakage in Emerging FET Architectures: Nanotube FETs Versus Nanowire FETs. IEEE Access 5, 18918–18926 (2017). https://doi.org/10.1109/ACCESS.2017.2751518

G. Musalgaonkar, S. Sahay, R.S. Saxena, M.J. Kumar, A Line Tunneling Field-Effect Transistor Based on Misaligned Core-Shell Gate Architecture in Emerging Nanotube FETs. IEEE Trans. Electron Devices 66(6), 2809–2816 (2019). https://doi.org/10.1109/TED.2019.2910156

R.K. Sharma, M. Gupta, R.S. Gupta, TCAD assessment of device design technologies for enhanced performance of nanoscale DG MOSFET. IEEE Trans. Electron Devices 58(9), 2936–2943 (2011). https://doi.org/10.1109/TED.2011.2160065

Y. Tsividis, and C. Mc Andrew, "Operation and Modeling of the MOS Transistor," Oxford Univ. Press, 2011.

S. Gundapaneni, S. Ganguly, A. Kottantharayil, Enhanced electrostatic integrity of short channel junctionless transistor with high-k spacers. IEEE Electron Device Lett. 32(10), 1325–1327 (2011). https://doi.org/10.1109/LED.2011.2162309

S. Sahay, M.J. Kumar, Controlling the drain side tunneling width to reduce ambipolar current in tunnel FETs using heterodielectric BOX. IEEE Trans. Electron Devices 62(11), 3882–3886 (2015). https://doi.org/10.1109/TED.2015.2478955

M. H. Na, E. J. Nowak, W. Haensch, and J. Cai, “The effective drive current in CMOS inverters,” in IEDM Tech. Dig., 2002, pp. 121–124. 10.1109/IEDM.2002.1175793.

R. Rios et al., Comparison of junctionless and conventional trigate transistors with Lg down to 26 nm. IEEE Electron Device Lett. 32(9), 1170–1172 (2011). https://doi.org/10.1109/LED.2011.2158978

H. Lu, A. Seabaugh, Tunnel field-effect transistors: State-of-theart. IEEE J. Electron Devices Soc. 2(4), 44–49 (2014). https://doi.org/10.1109/jeds.2014.2326622

S.H. Kim, S. Agarwal, Z.A. Jacobson, P. Matheu, C. Hu, T.-J.K. Liu, Tunnel field effect transistor with raised germanium source. IEEE Electron Device Lett. 31(10), 1107–1109 (2010). https://doi.org/10.1109/led.2010.2061214

A. K. Gupta, A. Raman and N. Kumar, “Cylindrical Nanowire-TFET with Core-Shell Channel Architecture: Design and Investigation”. Silicon, pp.1–8., 2019. doi:10.1007/s12633–019–00331–1

N. Kumar and A. Raman “Design and Analog Performance Analysis of Charge-Plasma Based Cylindrical GAA Silicon Nanowire Tunnel Field Effect Transistor”. Silicon, pp.1–8, 2019. doi: 10.1007/s12633–019–00355–7

N. Kumar and A. Raman “Low voltage charge-plasma based dopingless Tunnel Field Effect Transistor: analysis and optimization”. Microsystem technologies, pp.1–8, 2019. doi: 10.1007/s00542–019–04666-y

S. Shreya, A.H. Khan, N. Kumar, S.I. Amin, S. Anand, Core-Shell Junctionless Nanotube Tunnel Field Effect Transistor: Design and Sensitivity Analysis for Biosensing Application. IEEE Sens. J. 20(2), 672–679 (2019). https://doi.org/10.1109/JSEN.2019.2944885

S.-G. Hur et al., “A practical Si nanowire technology with nanowire-oninsulator structure for beyond 10nm logic technologies,” in IEDM Tech. Dig., 2013, pp. 26.5.1–26.5.4. doi: 10.1109/iedm.2013.6724698.

ATLAS User’s Manual, Version 5 (SILVACO, Santa Clara, CA, USA, 2011)

J. Patel, D. Sharma, S. Yadav, A. Lemtur, P. Suman, Performance improvement of nano wire TFET by hetero-dielectric and hetero-material: At device and circuit level. Microelectron. J. 85, 72–82 (2019). https://doi.org/10.1016/j.mejo.2019.02.004

G. Dewey et al., “Fabrication, characterization, and physics of III–V heterojunction tunneling Field Effect Transistors (H-TFET) for steep sub-threshold swing,” in IEDM Tech. Dig., 2011, pp. 33.6.1–33.6.4. doi: 10.1109/IEDM.2011.6131666.

K. Tomioka, M. Yoshimura, T. Fukui, Sub 60 mV/decade switch using an InAs nanowire–Si heterojunction and turn-on voltage shift with a pulsed doping technique. Nano Lett. 13(12), 5822–5826 (2013). https://doi.org/10.1021/nl402447h

R. Gandhi, Z. Chen, N. Singh, K. Banerjee, S. Lee, Vertical Si-nanowire n-type tunneling FETs with low subthreshold swing (≤ 50 mV/decade) at room temperature. IEEE Electron Device Lett. 32(4), 437–439 (2011). https://doi.org/10.1109/led.2011.2106757

A. N. Hanna and M. M. Hussain, “Si/Ge hetero-structure nanotube tunnel field effect transistor,” J. Appl. Phys., vol. 117, no. 1, 2015, Art. no. 014310. doi: 10.1063/1.4905423.

G. Musalgaonkar, S. Sahay, R. S. Saxena and M. J. Kumar, "Nanotube Tunneling FET With a Core Source for Ultrasteep Subthreshold Swing: A Simulation Study," in IEEE Transactions on Electron Devices, vol. 66, no. 10, pp. 4425–4432, Oct. 201910.1109/TED.2019.2933756

Author information

Authors and Affiliations

Corresponding author

Additional information

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

About this article

Cite this article

Gupta, A.K., Raman, A. Performance analysis of electrostatic plasma-based dopingless nanotube TFET. Appl. Phys. A 126, 573 (2020). https://doi.org/10.1007/s00339-020-03736-7

Received:

Accepted:

Published:

DOI: https://doi.org/10.1007/s00339-020-03736-7