Abstract

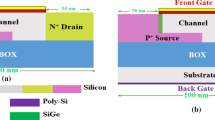

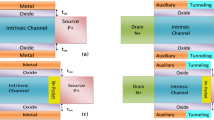

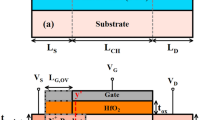

This paper investigates the trap analysis of a double-gate extended-source tunnel field-effect transistor (DG-ESTFET) and single-gate extended-source tunnel field-effect transistor (SG-ESTFET) with a δp+ SiGe pocket layer. The trap analysis of both structures is compared in terms of the currents, average subthreshold swing, threshold voltage, and switching ratio. In addition, the impact of interface trap charges at different interfaces on analog/RF performance, transfer characteristics, and slope are investigated and compared. It is observed that the trap charges between the silicon and front gate oxide interface (Si–HfO2) have a greater effect on the DG-ESTFET than the SG-ESTFET, whereas the reverse is true when trap charges are at the back gate oxide interface (Si–SiO2). In the case of analog/RF performance, the SG-ESTFET is found to be more affected by the trap charges at the silicon and front gate oxide interface (Si–HfO2).

Similar content being viewed by others

References

International Technology Roadmap for Semiconductors. http://www.maltiel-consulting.com/ITRS-2011-Executive-Summary.pdf. 2011

J. Madan and R. Chaujar, Appl. Phys. A 122, 973 (2016).

K.E. Moselund, D. Cutaia, H. Schmid, M. Borg, S. Sant, and H. Riel, IEEE Trans. Electron Devices 63, 1 (2016).

S. Kumar, E. Goel, K. Singh, B. Singh, M. Kumar, and S. Jit, IEEE Trans. Electron Devices 63, 8 (2016).

S. Kumar, E. Goel, K. Singh, B. Singh, P.K. Singh, K. Baral, and S. Jit, IEEE Trans. Electron Devices 64, 3 (2017).

J. Talukdar and K. Mummaneni, Appl. Phys. A 126, 81 (2020).

E. Goel, S. Kumar, K. Singh, B. Singh, M. Kumar, and S. Jit, IEEE Trans. Electron Devices 63, 3 (2016).

J. Talukdar, K. Mummaneni. (2019). https://doi.org/10.1007/s12633-019-00321-3.

J. Robertson, Microelectronic Eng. 86, 1558–1560 (2009). https://doi.org/10.1016/j.mee.2009.03.053.

M. Passlack, R. Droopad, and G. Brammertz, IEEE Trans. Electron Devices 57, 11 (2010).

A. Schenk, Solid-Store Electron. 35, 11 (1992).

S. Mookerjea, R. Krishnan, S. Datta, and V. Narayanan, IEEE Electron Device Lett. 30, 10 (2009).

C. Liu, S. Glass, G.V. Luong, K. Narimani, Q. Han, A.T. Tiedemann, A. Fox, W. Yu, X. Wang, S. Mantl, and Q.T. Zhao, IEEE Electron Device Lett. 38, 6 (2017).

C. Huang, T.Y. Hung, P.Y. Wang, and B.Y. Tsui, in International Symposium on Next-Generation Electronics (ISNE), Taipei (2015), pp. 1–2.

F. Mayer, C. L. Royer, J. F. Damlencourt, K. Romanjek, F. Andrieu, C. Tabone, B. Previtali, and S. Deleonibus, in 2008 IEEE International Electron Devices Meeting, (IEDM), (2008), pp. 1–5.

T.C.A.D. Synopsys, Manual, version. E2010.12.

A.O. Adan and K. Higashi, IEEE Trans. Electron Devices 48, 9 (2001).

D. Barah, A.K. Singh, and B. Bhowmick, Silicon 11, 2 (2019).

R.N. Sajjad, W. Chern, J.L. Hoyt, and D.A. Antoniadis, IEEE Trans. Electron Devices 63, 11 (2016).

M.G. Pala and D. Esseni, IEEE Trans. Electron Devices 60, 9 (2013).

S. Mookerjea, R. Krishnan, S. Datta, and V. Narayanan, IEEE Trans. Electron Devices 56, 9 (2009).

J. Madan and R. Chaujar, IEEE Trans. Electron Devices 64, 4 (2017).

P.G. Bahubalindruni, A. Kiazadeh, A. Sacchetti, J. Martins, A. Rovisco, V.G. Tavares, R. Martins, E. Fortunato, and P. Barquinha, J. Display Technol. 2, 6 (2016).

Author information

Authors and Affiliations

Corresponding author

Additional information

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

About this article

Cite this article

Talukdar, J., Rawat, G., Singh, K. et al. Comparative Analysis of the Effects of Trap Charges on Single- and Double-Gate Extended-Source Tunnel FET with δp+ SiGe Pocket Layer. J. Electron. Mater. 49, 4333–4342 (2020). https://doi.org/10.1007/s11664-020-08151-5

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s11664-020-08151-5