Abstract

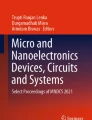

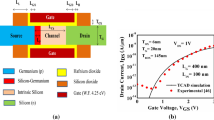

This communication presents the performance analysis and impact of low frequency flicker noise on a dual dielectric pocket heterojunction silicon on insulator (SOI) tunnel FET (TFET). The proposed TFET structure is well optimized for different gate-source underlap length and various thickness of δp+ Si1-xGex layer. It offers an ON current of 1.16 × 10−4 A/μm providing a high ON/OFF ratio of 3.49 × 1012 and a super steeper sub-threshold swing of 2 mV/dec. The device performance is investigated with concern to interface traps while both Uniform and Gaussian trap distributions are considered. The analyses specify that the proposed device is insusceptible to ON current degradation in presence of interface traps in comparison to OFF current behaviour. Electrical noise performance is examined in presence of interface traps and different mole fraction of germanium (Ge) in δp+ Si1-xGex layer. The device is further tested for its parasitic capacitances and transconductance to drain current ratio (gm/ID) behaviour. The high ratio of obtained gm/ID makes it compatible for future low power applications.

Similar content being viewed by others

References

Sarangi S, Bhushan S, Santra A, Dubey S, Jit S, Tiwari PK (2013) A rigorous simulation based study of gate misalignment effects in gate engineered double-gate (DG) MOSFETs. Superlattice Microst 60:263–279

Chaudhry A, Kumar MJ (2004) Controlling Short-Channel effects in deep-sub-micron SOI MOSFETs for improved reliability: a review. IEEE Trans Device Mater Reliab 4:99–109

Datta S, Liu H, Narayanan V (2014) Tunnel FET technology: a liability perspective. Micro electron. Reliab 54:861–874

Ortiz-Conde A, Garcia-Sanchez FJ, Muci J, Sucre-Gonzalez A, Martino JA, Der Agopian PG et al (2014) Threshold voltage extraction in tunnel FETs. Solid State Electron 93:49–55

Lu H, Esseni D, Seabaugh A (2015) Universal analytic model for tunnel FET circuit simulation. Solid State Electron 108:110–117

Boucart K, Ionescu AM (2007) Double-gate tunnel FET with high k gate dielectric. IEEE trans. Electron Devices 54:1725–1733

Zhaonian Yang, (2016 ) Tunnel Field-Effect Transistor With an L-Shaped Gate IEEE Electronic Device Letters 37

Sneh S, Jagadesh Kumar M (2011) Investigation of the novel attributes of a dual material gate Nanoscale tunnel field effect transistor. IEEE Trans on Electron Devices 58:404–410

Cao W, Yao CJ, Jiao GF, Huang Daming YHY, Ming-Fu L (2011) Improvement in reliability of tunneling field-effect transistor with p-n-i-n structure. IEEE Transactions on Electron Devices 58:2122–2126

Bhuwalka KK, Sedlmaier S (2004) Vertical tunnel field-effect transistor. IEEE Transactions on Electron Devices 51:279–282

Bahniman G, Mohammad WA (2013) Junctionless tunnel field effect transistor. IEEE Electron Devices Letters 34:584–586

Kao KH, William ASV, Vandenberghe G, et.al (2012) Direct and indirect band-to-band tunneling in germanium-based TFETs. IEEE Transactions Electron Devices 59:292–301

Mitra SK, Rupam G, Bhowmick B (2016) A hetero-dielectric stack gate SOI-TFET with Back gate and its application as a digital inverter. Superlattice Microst 92:37–51

Lv Y, Huang Q, Wang H, Chang S, He J (2016) A numerical study on grapheme nano ribbon heterojunction dual-material gate tunnel FET. IEEE Electron Device Lett 37:1354–1357

Chung SS (2012) The variability issues in small scale strained CMOS devices: random dopant and trap induced fluctuations. Proc. ISCDG: 107-111

Wang R et al (2013) A unified approach for trap-aware device/circuit co-design in nanoscale CMOS technology. IEDM Tech. Dig: 834-837

Jiao GF et al (2009) New degradation mechanisms and reliability performance in tunneling field effect transistors. Proc IEEE IEDM:1–4

Pandey R, Rajamohanan B et.al (2014) Electrical noise in Heterojunction Interband tunnel FETs. IEEE Transactions on Electron Devices 61: 552–560

Choi WY, Lee W (2010) Hetero-gate-dielectric tunneling field-effect transistors. IEEE Transactions on Electron Devices 57:2317–2319

Upasana NR, Saxena M, Gupta M (2016) Investigation of dielectric pocket induced variations in tunnel field effect transistor. Superlattice Microst 92:380–390

Bhuwalka KK, Schulze J, Ignaz E (2004) Performance enhancement of vertical tunnel field-effect transistor with SiGe in δp+ layer. Jpn J Appl Phys 43:4073–4078

Upasana NR, Saxena M, Gupta M (2019) Exploring the applicability of well optimized dielectric pocket tunnel transistor for future low power applications. Superlattice Microst 126:8–16

Zhang L Mansun Chan tunneling field effect transistor technology. Springer

User SD (2009). Synopsys:2009

Kim HW, Kim JH, Kim SW, Sun MC, Park E, Park BG (2014) Tunneling field effect transistor with Si/SiGe material for high current drivability. J Appl Phys. 53(6S): 06JE12-1-06JE12-4

Majumdar K, Rajaram S. Konjady, Tejas S Raj et al. (2011) Underlap optimization in HFinFET in presence of Interface traps. IEEE Trans Nanotechnol 10. https://doi.org/10.1109/TNANO.2011.2119401, 1249, 1253

Wei L, Hongxia L, Wang S, Shupeng C, Yang Z (2017) Design of High Performance Si/SiGe Heterojunction tunneling FETs with a T-shaped gate. Nanoscale Res Lett 12:198. https://doi.org/10.1186/s11671-017-1958-3

Biswas A, Dan SS, Royer CL, Grabinski W, Ionescu AM (2012) TCAD simulation of SOI TFETs and calibration of non-local band-to-band tunneling model. Micro Electron Eng 98:334–337

Wang W, Hwang J, Xuan Y, Ye PD (2011) Analysis of electron mobility in inversion-mode MOSFETs, IEEE Trans. Electron devices. 58: 1972-1978. https://doi.org/10.1109/TED.2011.2146255

Ghosh P, Bhowmick B (2018) Low-frequency noise analysis of heterojunction SELBOX TFET. Applied Physics A 124

Yingxin Q, Wang R, Qianqian H, Huang R (2014) A comparative study on the impacts of Interface traps on tunneling FET and MOSFET. IEEE Transactions on Electron Devices. 61(5):1284–1291

Hichem F, Fayçal D, Toufik B (2018) The role of the Ge mole fraction in improving the performance of a nanoscale junctionless tunneling FET: concept and scaling capability. Beilstein J. Nanotechnol 9:1856–1862. https://doi.org/10.3762/bjnano.9.177

Haartman Von M (2007) Low-frequency noise in advanced MOS devices

Nougier JP (1994) Fluctuations and noise of hot carriers in semiconductor materials and devices. IEEE trans. Electron Devices 41:2034–2049

Huang Q, Huang R, Chen C, Wu C, Wang J, Wang C et al (2014) Deep insights into low frequency noise behaviour of tunnel FETs with source junction engineering. Symposium on VLSI Technology, Digest of Technical Papers, pp 70–71

Rupam G, Brinda B, Baishya S (2016) Effect of scaling on noise in circular gate TFET and its application as a digital inverter. Microelectron J 53:16–24

Neves FS, Agopianand PGD, Martino JA, Cretu B, Rooyackers R, Vandooren A, Simoen E, Thean AV, Claeys C (2016) Low frequency noise analysis and modeling in vertical tunnel FETs with Ge source. IEEE Trans Electron Devices 63:1658–1665

Sweta C, Sanjeet SK, Sanjay K et al (2017) Temperature analysis of Ge/Si heterojunction SOI-tunnel FET. Superlattice Microst 110:162–170

Venkatesh P, Nigam K, Pandey S, Dj S, Kondekar NP (2017) Impact of Interface trap charges on performance of electrically doped tunnel FET with heterogeneous gate dielectric. IEEE Trans Device Mater Reliab 17(1):245–252

Madan J, Chaujar R (2017) Numerical simulation of N+ source pocket PIN-GAA-tunnel FET: impact of Interface trap charges and temperature. IEEE Transactions on Electron Devices 64(4):1482–1488

Leonardo B, Mariana S, Berardi RS (2015) TFET-based circuit design using the Transconductance generation efficiency gm/Id method. IEEE Journal of the Electron Devices Society 3:208–216

Author information

Authors and Affiliations

Corresponding author

Additional information

Publisher’s Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

About this article

Cite this article

Das, D., Chakraborty, U. A Study on Dual Dielectric Pocket Heterojunction SOI Tunnel FET Performance and Flicker Noise Analysis in Presence of Interface Traps. Silicon 13, 787–798 (2021). https://doi.org/10.1007/s12633-020-00488-0

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s12633-020-00488-0