Abstract

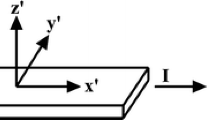

This paper covers the design, characterization and calibration of stress sensors useful to measure the in-plane stress at the surface of integrated circuits. Each sensor is based on piezo-FET current mirrors aligned in four different directions; the mismatch in the current output in each mirror is related to the stress aligned with the device, then, the changes in the output currents can be used to estimate both the magnitude and direction of uniaxial stress along the active area. The piezoFETs in the sensors are the same NMOS and PMOS transistors available in the IC technology, thus the device can be integrated into any CMOS process. Each kind of transistor has its sensitivity enhanced by a different component of the stress; the PMOS sensor reacts to the shear stress while the NMOS is sensitive to longitudinal stress. Compared with previous stress sensor designs based in piezoresistors, by using both PMOS and NMOS, it is possible to improve the estimation of the in-plane stress and isolate all the stress components. Symmetry and common-centroid are used in the layout to improve the match in the mirror; as a result, the design of a compact octagonal device is presented. The special layout and circuit design also allow canceling out out-of-plane components of the stress and other common-mode effects. Each sensor requires 40 × 60 µm2 total area and was fabricated using 0.6 µm CMOS technology. Samples of the devices were tested using a four-point bending test configuration to apply uniaxial stress. The experimental results show a linear relationship of the output current with the stress, which are in accordance with the piezoresistive effect theory. Using the differential output currents of both PMOS and NMOS piezo-FET current mirrors, it is possible to estimate the uniaxial stress magnitude and direction with an angle error lower than 4°. These kinds of piezoFET devices are suitable to determine the stress state in a local area, and several of them can be placed together in a stress-sensor matrix to map the stress on ICs.

Similar content being viewed by others

References

Suhling, J. C., & Jaeger, R. C. (2001). Silicon piezoresistive stress sensors and their application in electronic packaging. IEEE Sensors Journal, 1, 14–30.

Thompson, S. E., & Sun, G. (2006). Strained Si and the future direction of CMOS. In 2006 international symposium on VLSI technology, systems, and applications, 2006.

Popovic, R. S. (2010). Hall effect devices (2nd ed.). Abingdon: Taylor and Francis.

Jaeger, R. C., Ramani, R., Suhling, J. C., & Kang, Y. (1995). CMOS stress sensor circuits using piezoresistive field-effect transistors (PIFETs). In 1995 symposium on VLSI circuits, 1995. Digest of technical papers.

Hau, W. L. W., Yuen, M. M. F., Yan, G. Z., & Chan, P. C. H. (2000). A new stress chip design for electronic packaging applications. In International symposium on electronic materials and packaging, 2000. (EMAP 2000).

Fruett, F., & Meijer, G. C. M. (2010). The piezojunction effect in silicon integrated circuits and sensors. Berlin: Springer.

Smith, C. S. (1958). Macroscopic symmetry and properties of crystals. In F. Seitz & D. Turnbull (Eds.), Advances in research and applications (Vol. 6, pp. 175–249). Cambridge: Academic Press.

Gridchin, A. V. (2004). The four-terminal silicon piezotransducer: History and future. In 5th annual international Siberian workshop and tutorial on electron devices and materials.

Coraucci, G., & Fruett, F. (2007). A theoretical study of a novel multi-terminal pressure sensor based on the transversal piezoresistive effect. ECS Transactions, 9, 561–569.

Gieschke, P., Sbierski, B., & Paul, O. M. (2001). CMOS-based piezo-FET stress sensors in Wheatstone bridge configuration. In Sensors, 2011 IEEE, Limerick, Ireland.

Chen, Y., Jaeger, R. C., & Suhling, J. C. (2013). CMOS sensor arrays for high resolution die stress mapping in packaged integrated circuits. IEEE Sensors Journal, 13, 2066–2076.

Jaeger, R. C., & Suhling, J. C. (2018). First and second order piezoresistive characteristics of CMOS FETs: Weak through strong inversion. In 2018 48th European solid-state device research conference (ESSDERC), Dresden, Germany.

Chen, Y., Jaeger, R. C., & Suhling, J. C. (2006). Delta-sigma based CMOS stress sensor with RF output. In IEEE Asian solid-state circuits conference, 2006. ASSCC 2006.

Doelle, M., Peters, C., Ruther, P., & Paul, O. (2006). Piezo-FET stress-sensor arrays for wire-bonding characterization. Journal of Microelectromechanical Systems, 15(1), 120–130.

Ramirez, J. L., & Fruett, F. (2018). Multi-terminal piezoMOSFET sensor for stress measurements in silicon. In 31st symposium on integrated circuits and systems design (SBCCI), Bento Goncalves, Brazil.

XFAB. (2008). Datasheet 0.6 um CMOS Process. XC06: 0.6 micron modular mixed signal technology.

Ramirez, J., & Fruett, F. (2017). A compact eight-terminal piezotransducer for stress measurements in silicon. Journal of Integrated Circuits and Systems, 12, 24–32.

Matsuda, K., Suzuki, K., Yamamura, K., & Kanda, Y. (1993). Nonlinear piezoresistance effects in silicon. Journal of Applied Physics, 73, 1838–1847.

Kanda, Y. (1991). Piezoresistance effect of silicon. Sensors and Actuators A: Physical, 28, 83–91.

Cho, C. H., Jaeger, R. C., & Suhling, J. C. (2008). Characterization of the temperature dependence of the piezoresistive coefficients of silicon from − 150 C to + 125 C. IEEE Sensors Journal, 8, 1455–1468.

Lemke, B., Baumann, M., Gieschke, P., Baskaran, R., & Paul, O. (2013). Piezoresistive CMOS-compatible sensor for out-of-plane shear stress. Sensors and Actuators A: Physical, 189, 488–495.

Suhling, J. C., Jaeger, R. C., Lall, P., Rahim, M. K., Roberts, J. C., & Hussain, S. (2009). Application of stress sensing test chips to area array packaging. In 10th international conference on thermal, mechanical and multi-physics simulation and experiments in microelectronics and microsystems, 2009. EuroSimE 2009.

Baker, R. J. (2008). CMOS: Circuit design, layout, and simulation. Hoboken: Wiley.

Allen, P. E., & Holberg, D. R. (2002). CMOS analog circuit design. Oxford: Oxford University Press.

Sansen, W. M. C. (2006). Analog design essentials (the international series in engineering and computer science). Secaucus, NJ: Springer.

Gieschke, P., Sbierski, B., & Paul, O. M. (2011). Shear piezoresistance in MOSFET devices under general operating conditions. IEEE Transactions on Electron Devices, 58, 4145–4154.

Acknowledgements

The authors acknowledge Eldorado Institute and the Brazilian National Council of Scientific and Technological Development—CNPq by the financial support; to Ricardo Yoshioka and Jose Bertuzzo for the technical support and follow-ups. We are grateful to Ricardo Cotrin, Giuliani Maloni and the DEE staff at Centre of Information Technology CTI for the support in packaging and testing, to the Centre of Semiconductor components CCS-UNICAMP, for photographies and experimental setup.

Funding

This study was financed in part by the Coordenação de Aperfeiçoamento de Pessoal de Nível Superior—Brasil (CAPES)—Finance Code 001.

Author information

Authors and Affiliations

Corresponding author

Additional information

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

About this article

Cite this article

Ramirez, J.L., Fruett, F. Mechanical stress estimation using PiezoFET octagonal current mirrors. Analog Integr Circ Sig Process 106, 165–175 (2021). https://doi.org/10.1007/s10470-020-01647-4

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10470-020-01647-4