Abstract

The development of brain-inspired neuromorphic computing, including artificial intelligence (AI) and machine learning, is of considerable importance because of the rapid growth in hardware and software capacities, which allows for the efficient handling of big data. Devices for neuromorphic computing must satisfy basic requirements such as multilevel states, high operating speeds, low energy consumption, and sufficient endurance, retention and linearity. In this study, inorganic perovskite-type amorphous strontium vanadate (a-SrVOx: a-SVO) synthesized at room temperature is utilized to produce a high-performance memristor that demonstrates nonvolatile multilevel resistive switching and synaptic characteristics. Analysis of the electrical characteristics indicates that the a-SVO memristor illustrates typical bipolar resistive switching behavior. Multilevel resistance states are also observed in the off-to-on and on-to-off transition processes. The retention resistance of the a-SVO memristor is shown to not significantly change for a period of 2 × 104 s. The conduction mechanism operating within the Ag/a-SVO/Pt memristor is ascribed to the formation of Ag-based filaments. Nonlinear neural network simulations are also conducted to evaluate the synaptic behavior. These results demonstrate that a-SVO-based memristors hold great promise for use in high-performance neuromorphic computing devices.

Similar content being viewed by others

Introduction

The use of digital computing systems based on von Neumann architecture has led to the development of outstanding memory technologies following Moore’s law over the last several decades, with a consistent aim to manufacture integrated circuits with a higher number of transistors and a lower energy consumption within a smaller area. To achieve this, high-density and low-power computing system engineering is essential, but traditional Si-based devices face a number of physical limitations1, thus innovative computing architecture is required. In this vein, neuromorphic computing systems inspired by the human brain have been introduced and are considered a promising approach to overcoming the bottlenecks associated with conventional von Neumann computing systems2,3,4.

To construct neuromorphic computing systems, artificial memristor-based synapses that have their synaptic characteristics updated by electrical stimuli are arranged in a circuit5,6. With this structure in mind, resistive random access memory (RRAM) has emerged as a highly promising contender for use in future computing devices due to its great scalability, low energy consumption, quick switching (sub-ns), and simple two-terminal structure with a cell size of 4F2, where F is the minimum feature size1,7,8,9,10. Extensive research has thus been conducted on RRAM to take advantage of its high storage density and potential application in neuromorphic computing systems. Most resistive switching materials in RRAM exhibit two states: a low resistance state (LRS) and a high resistance state (HRS). This type of multilevel resistance allows the possibility of multilevel storage, which can provide more storage space within a single cell and generate synaptic behavior, leading to material and structural innovation11,12,13,14. Thus, researchers have made an effort to realize multilevel storage using a variety of approaches, including heterostructures15,16, the insertion of an interlayer17,18, and doping techniques19,20.

Various materials have been proposed for the active layer, such as binary oxides21,22,23, perovskite materials24,25,26,27,28, and organic materials29,30, and these materials exhibit different types of resistive switching mechanism under certain conditions. For instance, Pt/TiO2/Pt devices have been found to exhibit unipolar resistive switching behavior31, but modulation of the polarity of the electroforming in Pt/TiO2/Pt leads to bipolar reset32. In particular, perovskite-based switching behavior has been widely investigated because of the distinctive properties of this material. Most previous studies of perovskite-based RRAM have focused on metal-to-insulator (MIT) materials33,34. For example, bulk ABO3 has been reported to have a metallic nature with low electrical resistivity35, with the Hubbard model indicating that MIT systems behave as a Mott insulator under critical conditions35,36,37. MIT materials such as Ca2RuO4, (V1−xCrx)2O3, and Pr0.7Ca0.3MnO3 have been regularly investigated and have proven to be capable of resistive switching38,39,40. However, switching behavior can only be realized with high-temperature treatment and the use of specific substrates during fabrication, meaning these materials are unsuitable for complementary metal-oxide semiconductor (CMOS) processes, hampering the development of commercial MIT-based devices. For practical applications, fabrication has to be carried out at low temperatures, and CMOS-compatible substrates need to be employed. In this respect, it has been shown that nonstoichiometric perovskite-type oxides synthesized at room temperature can exhibit defect-related resistive switching characteristics, a general property of RRAM devices25,41.

In this study, we characterized the electrical performance of a metal-insulator-metal (MIM) structure in which an a-SVO thin film was sandwiched between bottom Pt and top Ag electrodes and evaluated its resistive switching characteristics at room temperature. Note that a perovskite-structured SrVO3 single-crystal thin film was used as a transparent conducting electrode because of its high electrical conductivity and high transmittance42. As compared to crystalline SrVO3, the sputtered a-SVO film has advantages, including large area thickness and composition uniformity, low temperature growth, structural and compositional variations by engineering the oxygen content43, excellent optical transparency in the near-ultraviolet (UV) region44, and outstanding flexibility. The a-SVO films exhibit a large bandgap and low electrical conductivity because V 3d orbitals dominantly affect the in-gap states near the Fermi energy, and the substantial distortion in the V-O6 octahedra causes an increase in the separation between the d|| orbitals and the π* band43,44,45. Our sputtered a-SVO film, which acted as an insulator, displayed nonvolatile resistive switching behavior, and reversible multilevel transitions were able to be controlled using voltage modulation. In addition, the synaptic behavior of the a-SVO film was investigated as a function of voltage stress in order to determine the suitability of the proposed a-SVO-based memristor for use in neuromorphic computing.

Results and Discussion

Nonlinear cyclic voltammetry of the a-SVO memristor

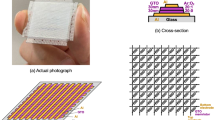

Fig. 1(a) displays a schematic diagram of the proposed a-SVO memristor. A 40-nm-thick a-SVO active layer is sandwiched between a Pt film as the bottom grounding electrode and an Ag film as the top terminal electrode (see the Experimental Section for more details). To examine the microstructure of the sputtered a-SVO, X-ray diffraction (XRD) analysis of a 100-nm-thick a-SVO thin film on a glass substrate was conducted (Fig. 1(b)). The XRD results revealed a broad intense peak at θ = ~22°, which is characteristic of the amorphous phase. Furthermore, Hall measurements showed that the a-SVO film had extremely high resistance at room temperature, indicating the lack of mobile charge carriers.

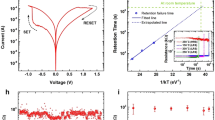

Fig. 2(a) presents the I-V curves of an Ag/a-SVO/Pt device derived from measurements taken at room temperature using a DC double ramp sweep for 100 cycles. To operate the a-SVO memristor, electroforming was conducted using voltage sweeping from 0 to 5 V with a compliance current (ICC) of 1 mA, as shown in the inset of Fig. 2(a). The I-V characteristics during the voltage sweeps are indicative of typical bipolar resistive switching behavior15,16,17,18,19,20. After the electroforming process, DC voltage sweeping from 0 V → 1 V → 0 V with an ICC of 1 mA resulted in a SET process (i.e., an off-to-on transition) and sweeping from 0 V → −0.7 V → 0 V without an ICC led to a RESET process (i.e., an on-to-off transition). A rapid increase in the current from an HRS to an LRS was observed for the SET process, while a gradual decrease in the current occurred from an LRS to an HRS for the RESET process without an ICC. It is important to note that, in the RESET process, the a-SVO device needed a higher negative current than the required ICC, which has been observed in previous results46. It is noted that variation of the resistances obtained from four randomly selected devices after 10 cycles (Fig. S1) indicates the uniform performance of different Ag/a-SVO/Pt-based devices.

An a-SVO-based memristor exhibiting bipolar resistive switching. (a) I-V properties of the Ag/a-SVO/Pt memristor after 100 consecutive DC cycles. The inset graph represents the electroforming process. (b) DC I-V properties with a positive bias and the corresponding slopes on a double-logarithmic scale. (c) ICC-modulated DC I-V curves with a positive bias and stop voltage-modulated DC I-V curves with a negative bias. The arrow denotes the sweep sequence. (d) Endurance testing up to 100 cycles at an LRS with an ICC of 1 mA and at HRSs with VSTOP = −0.7 and −1 V. (e) The distribution of the SET voltage. The inset indicates the distribution of the RESET voltage. (f) Retention testing up to 2 × 104 s at an LRS with an ICC of 1 mA, and at HRSs with VSTOP = −0.7 and −1 V.

To understand the conduction mechanism of the a-SVO memristor, a double-logarithmic scaled I-V curve was obtained (Fig. 2(b)). The fitted curve of the a-SVO memristor exhibited conduction behavior that was consistent with a typical trap-assisted space-charge-limited current47. In particular, three distinct regions representing different conduction mechanisms are observable in Fig. 2(b). In the low voltage region (<0.2 V), the slope of the fitted line is approximately 1.02 \((I\propto {V}^{1.02})\), which indicates Ohmic conduction. The region between 0.2 and 0.27 V has a slope of about 2.92 \((I\propto {V}^{2.92})\), indicating that Child’s law conduction is dominant. The third region between 0.27 and 0.3 V has a slope of over 14. These conduction mechanisms are typical of the phenomena observed for bipolar resistive switching devices48.

In order to emulate a synaptic device, the multilevel resistance properties of the a-SVO memristor were examined as a function of ICC in the range of 1 μA–1 mA and sweep stop voltages (VSTOP) in the range of −0.7 V to −2.2 V (Fig. 2(c)). Multilevel resistance states, i.e., analog switching behavior, were observed in the SET and RESET processes, which are essential electrical properties for neuromorphic computing applications49. Fig. 2(d) displays the resistance (corresponding to either LRS or two HRSs) as a function of the number of cycles. The LRS at ICC = 1 mA and the HRS at VSTOP = −0.7 V exhibit uniform resistance with little deviation. On the other hand, the resistance of the HRS at VSTOP = −1 V fluctuated significantly with an increasing number of cycles up to about 90, after which the variation becomes lower.

Fig. 2(e) presents the classical Gaussian distribution of the SET voltages for the two HRSs of the a-SVO memristor. The cycle-to-cycle variation of the HRS at VSTOP = −1 V is larger than that of the HRS at VSTOP = −0.7 V. This could be related to the fact that the former is more strongly affected by the thermal effect caused by the higher electric field. The variation in the RESET voltage (VRESET) is proportional to the distribution of the SET voltage (VSET), as shown in the inset of Fig. 2(e). Fig. 2(f) presents the retention test results of the a-SVO memristor for different resistance states measured at room temperature. Individual states were monitored at a read voltage of +0.1 V every 2 s, and no significant changes were observed for a period of 2 × 104 s. This is because the atomic migration of a conductive filament due to Joule heating rarely occurs under voltage stress50. These results indicate that the a-SVO memristor satisfies the requirements for use in potential synapse devices.

Conduction mechanisms for the a-SVO memristor

Time-of-flight secondary ion mass spectroscopy (ToF-SIMS) 3D mapping was utilized to determine the mechanisms responsible for the formation of the conductive filament because it represents a powerful tool for visualizing target behavior within complex structures51. Three-dimensional mapping of th Ag/a-SVO/Pt memristor was achieved via rasterizing over a 100 × 100 μm2 area using a Cs+ beam with an energy of 3 keV and a current of 30 nA after DC sweeping at ICC = 1 mA and VSTOP = −0.7 V for 100 cycles. Fig. 3(a)–(f) illustrates the spatially resolved 3D mapping images of the Ag/a-SVO/Pt memristor, with the color-coded element signals corresponding to Ag, Sr, V, O, and Pt. Fig. 3(g) displays the depth profiles of the Ag/a-SVO/Pt memristor, which was stressed using an electric field at room temperature. The mapping results revealed that Ag atoms had drifted through the a-SVO thin film and connected the top Ag electrode to the bottom Pt one (Fig. 3(b)). The conductive filament is depicted as a cone-shaped rod, with the diameter of the filament larger as it gets closer to the Ag electrode.

ToF-SIMS depth profiles of the Ag/a-SVO/Pt memristor after cyclic voltammetry. (a) Merged 3D mapping image of Ag, Sr, V, O, and Pt signals. (b–f) 3D mapping images of Ag, Sr, V, O, and Pt. A cone-shaped Ag conduction filament is observed in the a-SVO film, as marked by the dotted lines. (g) Depth profiles showing the distribution of the selected elements.

Fig. 4(a,b) presents the ultraviolet photoelectron spectroscopy (UPS) secondary electron cut-off (SECO) region and the valence band edge region, respectively of the a-SVO film on an Si substrate. The work function of the a-SVO thin film can be directly estimated using the SECO point by line-fitting the low kinetic energy and valence band edge regions52. To produce a band diagram for the Ag/a-SVO/Pt structure, the optical band gap energy was determined using the Tauc relation (αhν)2 vs hν, where α is the absorbance coefficient gained from UV-visible measurements, which is an accepted method for evaluating the optical band gap energy of amorphous materials53 (Fig. 4(c)). The optical bandgap and work function were calculated to be 4.3 eV and 3.1 eV, respectively. The electron affinity of the a-SVO film was also evaluated to be 1.6 eV using UPS. Our findings were consistent with previous results44, with the optical transmittance of crystalline SVO films rapidly dropping at wavelengths below 520 nm; however, the sputtered a-SVO thin films grown at room temperature did not experience a reduction in transmittance even at wavelengths below 400 nm.

UPS analysis of an a-SVO film. (a) UPS SECO region and (b) valence band edge region of the a-SVO film. (c) Tauc plot from UV-Vis analysis of the a-SVO film. The red line represents the fitting line in the linear region. (d) Schematic energy band diagram of the Ag/a-SVO/Pt memristor under forward voltage bias. The conduction of Ag atoms is dominated by hopping from traps near the valence band edges of the a-SVO film, which is pinned by the electrodes. At the electrode/a-SVO interfaces, redox-based reactions occur, where Ag atoms are ionized into Ag+ ions or the Ag+ ions are reduced back to Ag atoms.

Based on the band gaps, work functions, and electron affinities, Fig. 4(d) presents a band diagram of the Ag/a-SVO/Pt memristor. High double-Schottky barriers formed at the interfaces between the bottom Pt electrode (work function = 5.3 eV), the a-SVO film, and the top Ag electrode (4.7 eV). When a positive voltage was applied to the top Ag electrode and the bottom Pt one was grounded, the electric field was driven by the difference in the potential. With increasing voltage, Ag ions gradually appeared and dissolved into the a-SVO film, acting as an electrolyte. This amorphous electrolyte contained numerous point defects, trapping Ag+ or e−. The electric field caused these Ag+ ions to drift toward the bottom Pt electrode in an ion-hopping process4. The deposited Ag atoms then grew from the bottom Pt electrode to the Ag top electrode, forming a filament2,6,9. Consequently, the filament connected the two electrodes, converting the resistance of the a-SVO memristor from an HRS to an LRS (i.e., instigating the SET process). The thickness of the conductive filament can be controlled by modulating the current through the memristor, which means the conductance is adjustable. This feature is an essential requirement for a memristor to serve as a synaptic device.

A COMSOL Multiphysics s imulation was also carried out to further investigate the conduction mechanism involved in the Ag/a-SVO/Pt memristor54,55,56. To understand the RESET process, the thermal and electrical effects were taken into account in the simulations. The RESET process can be described by the following equations:

where nD, D, μ, ψ, σ, and kth are the concentration of Ag atoms, the diffusivity, the drift velocity, the external applied voltage at the Ag electrode, the electrical conductivity, and the thermal conductivity, respectively. In the simulation, the conductive filament and top Ag electrode were assumed to have a uniform Ag concentration (nD) of 1 × 1022 cm−3 along the direction of the electric field direction (i.e., the filament) for the SET state. When the DC voltage was increased, the current flowed locally through the conductive filament and the device temperature increased because of Joule heating. The bias-induced thermal energy lowered the potential energy for the hopping of Ag+ ions, enhancing Ag migration along the electric field. Fig. 5(a) presents 2D maps for nD at reverse biases ranging from 0 to −1.3 V, while Fig. 5(b) displays 1D profiles for nD along the z-axis (i.e., the conductive filament) during the gradual onset of the RESET process. As can be seen in the simulation results, the concentration of Ag atoms in the vicinity of the bottom Pt electrode decreased with increasing reverse bias, reducing the electrical conductivity of the a-SVO memristor. Consequently, the resistance of the memristor increased further during the RESET process.

Simulating the synaptic behavior of the a-SVO memristor

To mimic the synaptic behavior of the a-SVO memristor, its conductance transition characteristics were examined by modulating the bias (Fig. S2). Ten cycles consisting of 40 repeated potentiation pulses (P-pulses) at 1.8 V with a pulse width of 100 ns followed by 40 repeated depression pulses (D-pulses) at −1.8 V with a pulse width of 100 ns were applied to the a-SVO memristor. The readout of the current was simultaneously carried out for each pulse, with the duty ratio of all pulses fixed at 50%. The analog switching behavior, which exhibits a gradual conduction transition with minimal fluctuation, is shown in Fig. 6(a). The conductance of the a-SVO device increases with the P-pulses and decreases with the D-pulses. It can be seen that 40 weight states can be accurately controlled according to the number of P- or D-pulses. The conductance can be tuned by varying the amplitude, the width, the duty ratio, and the number of pulses. Moreover, for neuromorphic computing applications, lowering the energy consumption per synaptic spike (V2 × t times the conductance) of the memristor is a crucial requirement57. Thus, to develop synaptic devices with fast programming speeds, the pulse conditions need to be optimized. Fig. 6(b) presents the normalized conductance as a function of the number of P- or D-pulses. At both voltages, nonlinear normalized conductance behavior can be observed, with the voltage with a higher negative bias exhibiting a larger variation. Furthermore, the nonlinearity (NL) values for the depression and potentiation processes were characterized (Fig. S3). The NL values for the depression process (0.32–0.35) were larger than those for the potentiation process (0.10–0.15), as shown in Fig. 6(c). This indicates that the rupture of the conductive filament takes place more rapidly than its formation, which involves a more complicated process58.

(a) 10 cycles and (b) normalized conductance of potentiation/depression synaptic plasticity of the Ag/a-SVO/Pt memristor. The nonlinear fitting curves can be described using the equation \(G(n)={G}_{initial}+{A}_{1}\)\([1-\exp (-n/{\tau }_{1})]+{A}_{2}[1-\exp (-n/{\tau }_{2})]\). (c) NL values of the potentiation and depression processes. (d) The simulated accuracy and (e) synaptic weight maps of a 100 × 100 binary image as a function of asynchronous iterations. Two schemes are calculated: the ideal case (NL = 0) and our device (NL = 0.12 and 0.34).

To evaluate the associative memory of the a-SVO memristor for neuromorphic system applications, a Hopfield neural network (HNN) simulation59, which has been commonly used to investigate associative memories and parallel processing, was conducted using Python. With associative memory, certain received patterns can be stored in the form of connection strength within the neural network. Therefore, stored patterns can be successfully retrieved through associated states. All synapses of an HNN are fully connected so that each synapse has a direct connection with all other synapses. These connections have an associated connection strength between the synapses. In the HNN simulation in the present study, a sigmoid activation function was used to metamorphose the graded weight updates of the synapses for nonlinear synaptic behavior60. In the calculation, 100 × 100 synapses were used (i.e., a total of 10,000), which were trained by a simple binary image (black = 1 and white = 0) whose initial conductance was the noised normalized conductance. The input patterns were assumed to be polarized, and the weight matrix for the input pattern was calculated using Eq. (4) below:

where Xi is the vector constructed from the ith input pattern, W is the weight matrix of the input patterns, n is the number of patterns, and I is the unit matrix. The input patterns were also converted into a vector and multiplied. The trained synapses were asynchronously potentiated or depressed by weight updates receiving binary information. This operation was randomly selected, representing asynchronous updating, in order to mimic biological synapses. An ideal case in which the value of NL was 0 was also calculated to evaluate the characteristics of the a-SVO memristor. The accuracy of the calculations compared to the ideal case was determined using Eq. (5):

where Gtarget(i) and Gtrained(i) are the target and trained normalized conductance of the ith synapses, respectively, and m is the total number of synapses (Fig. 6(d)). In the ideal case, the accuracy was saturated at 89.7% within 100,000 iterations, while the accuracy of our simulated device was saturated at 86.8%. The reason why the accuracy of the ideal case was not saturated at 100% could be that, in our simulation, a sigmoid function was adopted, which produces a non-binary response, or a Hopfield network energy that is localized at certain minimum energy states61,62. The synaptic weight maps of 100 × 100 synapses for 0, 20,000, and 100,000 asynchronous iterations when NL = 0.12 for potentiation and NL = 0.34 for depression are presented in Fig. 6(e). These results show that the proposed a-SVO memristor can be successfully trained to recognize the input pattern.

Conclusion

In summary, a sputtered a-SVO film sandwiched between top Ag and bottom Pt electrodes successfully demonstrated nonvolatile multilevel resistive switching and synaptic behavior under DC and pulse voltage stresses. In particular, analog switching, an essential characteristic for use in synaptic devices, was realized by modulating the ICC in the forward bias and the VSTOP in the reverse bias. Based on the results of ToF-SIMS, UPS, and the COMSOL Multiphysics simulation, this conduction was attributable to the formation of Ag-based filaments. Nonlinear HNN simulations were also conducted to evaluate the synaptic properties of the a-SVO memristor. These results indicate that room-temperature sputtered a-SVO films have the potential for use in high-performance nonvolatile memory or neuromorphic computing devices, and offer the possibility of using amorphous inorganic perovskite for information storage.

Methods

a-SVO memristor fabrication process

To fabricate the proposed a-SVO-based RRAM device, a commercial wet-oxidized SiO2 (300 nm)/Si substrate was adopted. This substrate was cleaned with acetone, methanol, and deionized water to remove contaminants from the surface for 5 min per cleaning agent. A 100-nm-thick Pt thin film was then deposited as the bottom electrode, followed by a 10-nm Ti adhesion layer, using e-beam evaporation. This was followed by a 40-nm-thick a-SVO thin film, which was deposited using an RF sputtering system with a 2-inch polycrystalline SrVO3 target (atomic ratio Sr:V:O = 1:1:3). The a-SVO thin film was deposited at room temperature under the following conditions: an RF sputtering power of 60 W, a working pressure of 1.33 Pa, and an Ar flow rate of 23 sccm. Finally, a 150-nm-thick top Ag electrode was added using RF sputtering with a patterned shadow mask.

Electrical measurements

A standard DC voltage sweep and retention test for multilevel states in the proposed Ag/a-SVO/Pt memristor was conducted using an Agilent 4155 C Semiconductor Parameter Analyzer, with the voltage bias applied to the top Ag and bottom Pt electrodes at room temperature. Pulse measurement was performed using a pulse generator (Agilent 81101 A) with a four-channel oscilloscope (Hantek 6254bd).

Optical and chemical characterizations

To plot the Tauc relation, the absorbance of a 100-nm-thick a-SVO film on a sapphire substrate was measured using a UV-visible spectrometer (UV-1800, Shimadzu) in the range of 200–900 nm. The crystal structure of the a-SVO was assessed with X-ray diffraction (XRD, SmartLab, Rigaku) in the range of 20–90° at a speed of 5°/min with a step size of 0.02°. A Cu target (λ = 1.5412 Å) was used as the X-ray source. The work function of the a-SVO was determined using UPS (AXIS SUPRA, Kratos). To investigate the conductive filament, ToF-SIMS (TOF.SIMS-5, ION-TOF, Münster, Germany) was used with a rastered Cs+ beam with an energy of 3 keV and a current of 30 nA (raster size: 300 μm × 300 μm).

References

Lee, W. H., Osakama, T., Asada, K. & Sugano, T. Design Methodology and Size Limitations of Submicrometer Mosfets for Dram Application. IEEE Trans. Electron Devices 35, 1876–1884, https://doi.org/10.1109/16.7400 (1988).

Burr, G. W. et al. Neuromorphic computing using non-volatile memory. Adv. Phys.-X 2, 89–124, https://doi.org/10.1080/23746149.2016.1259585 (2017).

Jo, S. H. et al. Nanoscale Memristor Device as Synapse in Neuromorphic Systems. Nano Lett. 10, 1297–1301, https://doi.org/10.1021/nl904092h (2010).

Yang, J. J. S., Strukov, D. B. & Stewart, D. R. Memristive devices for computing. Nat. Nanotechnol. 8, 13–24, https://doi.org/10.1038/nnano.2012.240 (2013).

Indiveri, G. & Liu, S. C. Memory and Information Processing in Neuromorphic Systems. Proc. IEEE 103, 1379–1397, https://doi.org/10.1109/jproc.2015.2444094 (2015).

Wang, Z. R. et al. Memristors with diffusive dynamics as synaptic emulators for neuromorphic computing. Nat. Mater. 16, 101–108, https://doi.org/10.1038/nmat4756 (2017).

Jeong, D. S. et al. Emerging memories: resistive switching mechanisms and current status. Rep. Prog. Phys. 75, 31, https://doi.org/10.1088/0034-4885/75/7/076502 (2012).

Meena, J. S., Sze, S. M., Chand, U. & Tseng, T. Y. Overview of emerging nonvolatile memory technologies. Nanoscale Res. Lett. 9, 33, https://doi.org/10.1186/1556-276x-9-526 (2014).

Wong, H. S. P. et al. Metal-Oxide RRAM. Proc. IEEE 100, 1951–1970, https://doi.org/10.1109/jproc.2012.2190369 (2012).

Yu, S. M. et al. A Low Energy Oxide-Based Electronic Synaptic Device for Neuromorphic Visual Systems with Tolerance to Device Variation. Adv. Mater. 25, 1774–1779, https://doi.org/10.1002/adma.201203680 (2013).

Pershin, Y. V. & Di Ventra, M. Experimental demonstration of associative memory with memristive neural networks. Neural Networks 23, 881–886, https://doi.org/10.1016/j.neunet.2010.05.001 (2010).

Wang, Z. Q. et al. Synaptic Learning and Memory Functions Achieved Using Oxygen Ion Migration/Diffusion in an Amorphous InGaZnO Memristor. Adv. Funct. Mater. 22, 2759–2765, https://doi.org/10.1002/adfm.201103148 (2012).

Kim, H., Sah, M. P., Yang, C. J., Roska, T. & Chua, L. O. Neural Synaptic Weighting With a Pulse-Based Memristor Circuit. IEEE Trans. Circuits Syst. I-Regul. Pap. 59, 148–158, https://doi.org/10.1109/tcsi.2011.2161360 (2012).

van de Burgt, Y. et al. A non-volatile organic electrochemical device as a low-voltage artificial synapse for neuromorphic computing. Nat. Mater. 16, 414–418, https://doi.org/10.1038/nmat4856 (2017).

Stathopoulos, S. et al. Multibit memory operation of metal-oxide bi-layer memristors. Sci. Rep. 7, 17532, https://doi.org/10.1038/s41598-017-17785-1 (2017).

Zhou, W. P. et al. Multilevel Resistance Switching Memory in La2/3Ba1/3MnO3/0.7 Pb(Mg1/3Nb2/3)O3-0.3PbTiO3 (011) Heterostructure by Combined Straintronics-Spintronics. ACS Appl. Mater. Interfaces 8, 5424–5431, https://doi.org/10.1021/acsami.5b11392 (2016).

Ma, G. K. et al. Ultra-high ON/OFF ratio and multi-storage on NiO resistive switching device. J. Mater. Sci. 52, 238–246, https://doi.org/10.1007/s10853-016-0326-5 (2017).

Wang, Y. et al. Investigation of resistive switching in Cu-doped HfO2 thin film for multilevel non-volatile memory applications. Nanotechnology 21, 6, https://doi.org/10.1088/0957-4484/21/4/045202 (2010).

Sedghi, N. et al. The role of nitrogen doping in ALD Ta2O5 and its influence on multilevel cell switching in RRAM. Appl. Phys. Lett. 110, 5, https://doi.org/10.1063/1.4978033 (2017).

Sedghi, N. et al. Enhanced switching stability in Ta2O5 resistive RAM by fluorine doping. Appl. Phys. Lett. 111, 5, https://doi.org/10.1063/1.4991879 (2017).

Sokolov, A. S. et al. Influence of oxygen vacancies in ALD HfO2−x thin films on non-volatile resistive switching phenomena with a Ti/HfO2−x/Pt structure. Appl. Surf. Sci. 434, 822, https://doi.org/10.1016/j.apsusc.2017.11.016 (2018).

Abdul Hadi, S. et al. Bipolar Cu/HfO2/p++ Si Memristors by Sol-Gel Spin Coating Method and Their Application to Environmental Sensing. Sci. Rep. 9, 9983, https://doi.org/10.1038/s41598-019-46443-x (2019).

Long, S. B. et al. Voltage and Power-Controlled Regimes in the Progressive Unipolar RESET Transition of HfO2-Based RRAM. Sci. Rep. 3, 8, https://doi.org/10.1038/srep02929 (2013).

Messerschmitt, F., Kubicek, M., Schweiger, S. & Rupp, J. L. M. Memristor Kinetics and Diffusion Characteristics for Mixed Anionic-Electronic SrTiO3-δ Bits: The Memristor-Based Cottrell Analysis Connecting Material to Device Performance. Adv. Funct. Mater. 24, 7448–7460, https://doi.org/10.1002/adfm.201402286 (2014).

Nili, H. et al. Nanoscale Resistive Switching in Amorphous Perovskite Oxide (a-SrTiO3) Memristors. Adv. Funct. Mater. 24, 6741–6750, https://doi.org/10.1002/adfm.201401278 (2014).

Heo, J. H. et al. Memory effect behavior with respect to the crystal grain size in the organic-inorganic hybrid perovskite nonvolatile resistive random access memory. Sci. Rep. 7, 16586, https://doi.org/10.1038/s41598-017-16805-4 (2017).

Liu, D. J. et al. Flexible All-Inorganic Perovskite CsPbBr3 Nonvolatile Memory Device. ACS Appl. Mater. Interfaces 9, 6171–6176, https://doi.org/10.1021/acsami.6b15149 (2017).

Lin, Q. Q. et al. Transient Resistive Switching Memory of CsPbBr3 Thin Films. Adv. Electron. Mater. 4, 7, https://doi.org/10.1002/aelm.201700596 (2018).

Lee, B. H. et al. Direct Observation of a Carbon Filament in Water-Resistant Organic Memory. ACS Nano 9, 7306–7313, https://doi.org/10.1021/acsnano.5b02199 (2015).

Minnekhanov, A. A. et al. Parylene Based Memristive Devices with Multilevel Resistive Switching for Neuromorphic Applications. Sci. Rep. 9, 10800, https://doi.org/10.1038/s41598-019-47263-9 (2019).

Rohde, C. et al. Identification of a determining parameter for resistive switching of TiO2 thin films. Appl. Phys. Lett. 86, https://doi.org/10.1063/1.1968416 (2005).

Jeong, D. S., Schroeder, H. & Waser, R. Coexistence of bipolar and unipolar resistive switching behaviors in a Pt/TiO2/Pt stack. Electrochem. Solid State Lett. 10, G51–G53, https://doi.org/10.1149/1.2742989 (2007).

Cario, L., Vaju, C., Corraze, B., Guiot, V. & Janod, E. Electric-Field-Induced Resistive Switching in a Family of Mott Insulators: Towards a New Class of RRAM Memories. Adv. Mater. 22, 5193–5197, https://doi.org/10.1002/adma.201002521 (2010).

Imada, M., Fujimori, A. & Tokura, Y. Metal-insulator transitions. Rev. Mod. Phys. 70, 1039–1263, https://doi.org/10.1103/RevModPhys.70.1039 (1998).

Anisimov, V. I., Zaanen, J. & Andersen, O. K. Band Theory and Mott Insulators - Hubbard-U Instead of Stoner-I. Phys. Rev. B 44, 943–954, https://doi.org/10.1103/PhysRevB.44.943 (1991).

Liechtenstein, A. I., Anisimov, V. I. & Zaanen, J. Density-Functional Theory and Strong-Interactions - Orbital Ordering in Mott-Hubbard Insulators. Phys. Rev. B 52, R5467–R5470, https://doi.org/10.1103/PhysRevB.52.R5467 (1995).

McWhan, D. B. & Remeika, J. P. Metal-insulator transition in (V1−xCrx)2O3. Phys. Rev. B: Solid State 2, 3734–3750, https://doi.org/10.1103/PhysRevB.2.3734 (1970).

Nakatsuji, S., Ikeda, S. I. & Maeno, Y. Ca2RuO4: New Mott insulators of layered ruthenate. J. Phys. Soc. Jpn. 66, 1868–1871, https://doi.org/10.1143/jpsj.66.1868 (1997).

Querré, M. et al. Non-volatile resistive switching in the Mott insulator (V1−xCrx)2O3. Physica B Condens. Matter 536, 327–330, https://doi.org/10.1016/j.physb.2017.10.060 (2018).

Lee, W. et al. Improved switching characteristics of perovskite oxide-based resistance random access memory by high-pressure oxygen annealing at low temperature. Phys. Status Solidi A-Appl. Mat. 208, 202–205, https://doi.org/10.1002/pssa.201026559 (2011).

Waser, R., Dittmann, R., Staikov, G. & Szot, K. Redox-Based Resistive Switching Memories - Nanoionic Mechanisms, Prospects, and Challenges. Adv. Mater. 21, 2632–2663, https://doi.org/10.1002/adma.200900375 (2009).

Zhang, L. et al. Correlated metals as transparent conductors. Nat. Mater. 15, 204–210, https://doi.org/10.1038/nmat4493 (2016).

Hui, S. Q. & Petric, A. Conductivity and stability of SrVO3 and mixed perovskites at low oxygen partial pressures. Solid State Ion. 143, 275–283, https://doi.org/10.1016/s0167-2738(01)00870-0 (2001).

Boileau, A. et al. Optical and electrical properties of the transparent conductor SrVO3 without long-range crystalline order. Appl. Phys. Lett. 112, 4, https://doi.org/10.1063/1.5016245 (2018).

Jung, D. H., So, H. S. & Lee, H. Structural and electrical properties of transparent conductor SrVO3 thin films grown using radio frequency sputtering deposition. J. Vac. Sci. Technol. A 37, 8, https://doi.org/10.1116/1.5054666 (2019).

Kinoshita, K. et al. Reduction in the reset current in a resistive random access memory consisting of NiOx brought about by reducing a parasitic capacitance. Appl. Phys. Lett. 93, 3, https://doi.org/10.1063/1.2959065 (2008).

Rose, A. Space-Charge-Limited Currents in Solids. Phys. Rev. 97, 1538–1544, https://doi.org/10.1103/PhysRev.97.1538 (1955).

Kim, K. M. et al. A detailed understanding of the electronic bipolar resistance switching behavior in Pt/TiO2/Pt structure. Nanotechnology 22, 8, https://doi.org/10.1088/0957-4484/22/25/254010 (2011).

Pershin, Y. V. & Di Ventra, M. Practical Approach to Programmable Analog Circuits With Memristors. IEEE Trans. Circuits Syst. I-Regul. Pap. 57, 1857–1864, https://doi.org/10.1109/tcsi.2009.2038539 (2010).

Rana, A. M. et al. Endurance and Cycle-to-cycle Uniformity Improvement in Tri-Layered CeO2/Ti/CeO2 Resistive Switching Devices by Changing Top Electrode Material. Sci Rep 7, 15, https://doi.org/10.1038/srep39539 (2017).

Choi, J. Y. et al. Effect of Si on the Energy Band Gap Modulation and Performance of Silicon Indium Zinc Oxide Thin-Film Transistors. Sci. Rep. 7, 8, https://doi.org/10.1038/s41598-017-15331-7 (2017).

Viezbicke, B. D., Patel, S., Davis, B. E. & Birnie, D. P. Evaluation of the Tauc method for optical absorption edge determination: ZnO thin films as a model system. Phys. Status Solidi B-Basic Solid State Phys. 252, 1700–1710, https://doi.org/10.1002/pssb.201552007 (2015).

Kia, A. M. et al. ToF-SIMS 3D Analysis of Thin Films Deposited in High Aspect Ratio Structures via Atomic Layer Deposition and Chemical Vapor Deposition. Nanomaterials 9, 14, https://doi.org/10.3390/nano9071035 (2019).

Larentis, S., Nardi, F., Balatti, S., Gilmer, D. C. & Ielmini, D. Resistive Switching by Voltage-Driven Ion Migration in Bipolar RRAM-Part II: Modeling. IEEE Trans. Electron Devices 59, 2468–2475, https://doi.org/10.1109/ted.2012.2202320 (2012).

Kim, S. et al. Physical electro-thermal model of resistive switching in bi-layered resistance-change memory. Sci. Rep. 3, 6, https://doi.org/10.1038/srep01680 (2013).

Srivastava, S., Dey, P., Asapu, S. & Maiti, T. Role of GO and r-GO in resistance switching behavior of bilayer TiO2 based RRAM. Nanotechnology 29, 11, https://doi.org/10.1088/1361-6528/aae135 (2018).

Menzel, S. et al. Origin of the Ultra-nonlinear Switching Kinetics in Oxide-Based Resistive Switches. Adv. Funct. Mater. 21, 4487–4492, https://doi.org/10.1002/adfm.201101117 (2011).

Yang, Y. C. et al. Observation of conducting filament growth in nanoscale resistive memories. Nat. Commun. 3, 8, https://doi.org/10.1038/ncomms1737 (2012).

Hopfield, J. J. Neural Networks and Physical Systems with Emergent Collective Computational Abilities. Proc. Natl. Acad. Sci. USA 79, 2554–2558, https://doi.org/10.1073/pnas.79.8.2554 (1982).

Hopfield, J. J. & Tank, D. W. Computing with neural circuits - A Model. Science 233, 625–633, https://doi.org/10.1126/science.3755256 (1986).

Mathias, A. C. & Rech, P. C. Hopfield neural network: The hyperbolic tangent and the piecewise-linear activation functions. Neural Networks 34, 42–45, https://doi.org/10.1016/j.neunet.2012.06.006 (2012).

Hopfield, J. J. Neurons with Graded Response Have Collective Computational Properties Like those of 2-State Neurons. Proc. Natl. Acad. Sci. USA 81, 3088–3092, https://doi.org/10.1073/pnas.81.10.3088 (1984).

Acknowledgements

This work was supported by the National Research Foundation (NRF) of Korea funded by the Ministry of Science and ICT (NRF-2017K1A1A2013160).

Author information

Authors and Affiliations

Contributions

T.-J.L., S.-K.K. and T.-Y.S. conceived the idea and designed this work. T.-J.L. fabricated the devices and performed most of the measurements. S.-K.K. contributed to the figure processing and contributed to some of the measurements. All the authors discussed and analyzed the results. T.-J.L. and T.-Y.S. wrote the manuscript. T.-Y.S. supervised this work.

Corresponding author

Ethics declarations

Competing interests

The authors declare no competing interests.

Additional information

Publisher’s note Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Supplementary information

Rights and permissions

Open Access This article is licensed under a Creative Commons Attribution 4.0 International License, which permits use, sharing, adaptation, distribution and reproduction in any medium or format, as long as you give appropriate credit to the original author(s) and the source, provide a link to the Creative Commons license, and indicate if changes were made. The images or other third party material in this article are included in the article’s Creative Commons license, unless indicated otherwise in a credit line to the material. If material is not included in the article’s Creative Commons license and your intended use is not permitted by statutory regulation or exceeds the permitted use, you will need to obtain permission directly from the copyright holder. To view a copy of this license, visit http://creativecommons.org/licenses/by/4.0/.

About this article

Cite this article

Lee, TJ., Kim, SK. & Seong, TY. Sputtering-deposited amorphous SrVOx-based memristor for use in neuromorphic computing. Sci Rep 10, 5761 (2020). https://doi.org/10.1038/s41598-020-62642-3

Received:

Accepted:

Published:

DOI: https://doi.org/10.1038/s41598-020-62642-3

This article is cited by

Comments

By submitting a comment you agree to abide by our Terms and Community Guidelines. If you find something abusive or that does not comply with our terms or guidelines please flag it as inappropriate.