Abstract

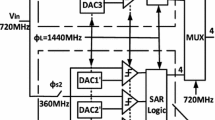

A successive-approximation-register (SAR) analog-to-digital converter (ADC) topology is presented, which optimizes the time distribution during the conversion. It is based on the semi-synchronous timing and uses a delay-looked loop (DLL) for clock generation. The absence of timing determined by analog delays allows an increase of the conversion speed compared to an asynchronous ADC using the same digital-to-analog converter (DAC), comparator and SAR logic. The results of circuit simulations on transistor level confirm the proper operation of the proposed approach.

Similar content being viewed by others

References

Kuttner, F. (2002). A 1.2 V 10 b 20 M Sample/s non-binary successive approximation ADC in 0.13 μm CMOS. In IEEE international solid-state circuits conference (pp. 176–177).

Promitzer, G. (2000). 12 bit low power fully differential switched capacitor non-calibrating successive approximation ADC with 1 MS/s. In Proceedings of the 26th European solid-state circuits conference (pp. 176–179).

Tong, T., Hanumolu, P., & Temes, G. (2012). A semi-synchronous SAR ADC. Analog Integrated Circuits and Signal Processing,71(3), 407–410.

Chen, S. W. M., & Brodersen, R. W. (2006). A 6-bit 600-MS/s 5.3-mW asynchronous ADC in 0.13-μm CMOS. IEEE Journal of Solid-State Circuits,41(12), 2669–2680.

Raj, G., Gupta A., & Gupta A. (2013). Self timed high speed 8-bit SAR ADC in 0.35 μm. In Annual IEEE India conference (pp. 1–6).

Janke, D., et al. (2019). A 9-Bit 10-MHz 28-μW SAR ADC Using Tapered Bit Periods and a Partially Interdigitated DAC. IEEE Transactions on Circuits and Systems II: Express Briefs,66(2), 187–191.

Craninckx, J., & van der Plas, G. (2007). A 65 fJ/conversion-step 0-to-50 MS/s 0-to-0.7 mW 9b charge-sharing SAR ADC in 90 nm digital CMOS. In IEEE international solid-state circuits conference (pp. 246–247).

Ginsburg, B. P., & Chandrakasan, A. (2006). A 500-MS/s 5-b ADC in 65-nm CMOS. In IEEE Symposium on VLSI Circuits (pp. 140–141).

Fotouhi, B., & Hodges, D. (1979). High-resolution A/D conversion in MOS/LSI. IEEE Journal of Solid-State Circuits,14(6), 920–926.

Cho, T. B., & Gray P. R. (1994). A 10-bit, 20-MS/s, 35-mW pipeline A/D converter. In IEEE Custom Integrated Circuits Conference (pp. 499–502).

Dessouky, M., & Kaiser, A. (2001). Very low-voltage digital audio TR modulator with 88-dB dynamic range using local switch bootstrapping. IEEE Journal of Solid-State Circuits,36(3), 349–355.

van Elzakker, M., et al. (2010). A 10-bit charge-redistribution ADC consuming 1.9 μW at 1 MS/s. IEEE Journal of Solid-State Circuits,45(5), 1007–1015.

Author information

Authors and Affiliations

Corresponding author

Additional information

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

About this article

Cite this article

Panov, G., Popov, A. A semi-synchronous SAR ADC with variable DAC settling time using a DLL. Analog Integr Circ Sig Process 103, 187–194 (2020). https://doi.org/10.1007/s10470-020-01603-2

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10470-020-01603-2