Abstract

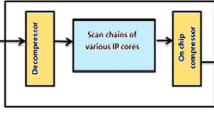

The objective of this research is the assessment of circuit design compression strategy carrying a greater number of similar output chains. The proposed method decreases the testing time while keeping lesser area overhead. The decompression technique depends upon constant LFSR diffusion which is utilized as a part of such a route, to the point that it empowers LFSR lockout getting away inside the least amount of clock series. It involves a different scheming of the LFSR de-compressor and the output set timer inputs. The proposed work presents the tetrad state skip decompression adequacy for various LFSR dimensions, examine chain measurements and quantities of similar LFSR data. Our observations depict that it is equipment sparing to utilize an LFSR by skipping individual states as opposed to employing an LFSR deceased along with a stage shifter. In other words, it uses a lesser amount of interior XOR doors, ensures most last partition between sweep chains without presenting any additional postponement on the LFSR outcomes. Exploratory outcomes have demonstrated that the displayed test design decompression on conventional circuits gives an unlimited blame scope and lesser test duration besides the minor equipment overhead is contrasting the forms composed and the assistance of the recent days’ mechanical instruments.

Similar content being viewed by others

Change history

09 May 2022

This article has been retracted. Please see the Retraction Notice for more detail: https://doi.org/10.1007/s10617-022-09261-5

References

Reda S, Orailoglu A (2002) Reducing test application time through test data mutation encoding. In: Proceedings design, automation and test in Europe, conference and exhibition (DATE 02). IEEE CS Press, pp 387–393

Koenemann B, Barnhart C, Keller B, Snethen T, Farnsworth O, Wheater D (2001) A smart BIST variant with guaranteed encoding. In: 10th Asian test symposium, proceedings, pp 325–330

Chandra A, Chakrabarty K (2003) Test data compression and test resource partitioning for system-on-a-chip using frequency-directed run-length (FDR) codes. IEEE Trans Comput 52(8):1076–1088

Würtenberger A, Tautermann CS, Hellebrand S (2004) Data compression for multiple scan chains using dictionaries with corrections. In: Proceedings of international test conference (ITC 04). IEEE CS Press, pp 926–935

Wang Z, Chakrabarty K (2005) Test data compression for IP embedded cores using selective encoding of scan slices. In: Proceedings of international test conference (ITC 05). IEEE Press, pp 581–590

Balakrishnan KJ, Touba NA (2006) Improving linear test data compression. IEEE Trans Very Large Scale Integr VLSI Syst 14(11):1227–1237

Lee J, Touba NA (2007) LFSR-reseeding scheme achieving low-power dissipation during test. IEEE Trans Comput Aided Des Integr Circuits Syst 26(2):396–401

Larsson A, Larsson E, Chakrabarty K, Eles P, Peng Z (2008) Test-architecture optimization and test scheduling for SOCs with core-level expansion of compressed test patterns. In: Design, automation and test in Europe, 2008. DATE’08, pp 188–193

Mrugalski G, Mukherjee N, Rajski J, Czysz D, Tyszer J (2009) Compression based on deterministic vector clustering of incompatible test cubes. In: Test international conference, pp 1–10

Chen M, Mishra P, Kalita D (2010) Efficient test case generation for validation of UML activity diagrams. Des Autom Embed Syst 14(2):105–130

Czysz D, Mrugalski G, Mukherjee N, Rajski J, Szczerbicki P, Tyszer J (2011) Deterministic clustering of incompatible test cubes for higher power-aware EDT compression. IEEE Trans Comput Aided Des Integr Circuits Syst 30(8):1225–1238

Singha B, Khoslab A, Narangc SB (2012) Area overhead and power analysis of march algorithms for MBIST. Int Conf Commun Technol Syst Des 30:930–936

Noor NQM, Yusof Y, Saparon A (2009) Low area FSM based memory BIST for synchronous SRAM. In: 2009 5th international colloquium on signal processing & its applications, pp 409–412

Mosin SG, Chebykina NV, Serina MS (2011) Technique of LFSR based test generator synthesis for deterministic and pseudorandom testing. In: 2011 11th international conference the experience of designing and application of CAD systems in microelectronics (CADSM), pp 128–131

Voyiatzis I, Efstathiou C, Antonopoulou H, Milidonis A (2013) An effective two-pattern test generator for arithmetic BIST. Elsevier J Comput Electr Eng 39:398–409

Krishnan KM, Sailaja M (2014) Low power memory BIST address generator using clock controlled LFSR. J Electron Test 30(1):77–85

Novák O, Jenícek J, Rozkovec M (2016) Test decompressor effectivity improvement. In: Digital system design (DSD), 2016 Euromicro conference, 31 Aug–2 Sept

Chen J-Z, Lee K-J (2017) Test stimulus compression based on broadcast scan with one single input. IEEE Trans Comput Aided Des Integr Circuits Syst 36(1):184–197

Basu K, Mishra P (2010) Test data compression using efficient bitmask and dictionary selection methods. IEEE Trans Very Large Scale Integr VLSI Syst 18(9):1277–1286

Mehta US, Dasgupta KS, Devashrayee NM (2010) Hamming distance based reordering and column wise bit stuffing with difference vector: a better scheme for test data compression with run length based codes. In: 23rd international conference on VLSI design

Sharma D, Ghosh D, Vohra H (2012) Test data volume minimization using double hamming distance reordering with mixed RL Huffman based compression scheme for System-on-chip. In: Nirma University international conference on engineering, NUiCONE-2012, pp 6–8

Lee L-J, Tseng W-D, Lin R-B, Chang C-H (2012) 2\(n\) Pattern run-length for test data compression. IEEE Trans Comput Aided Des Integr Circuits Syst 31(4):644–648

Sidmanoglou P, Nikolos D (2013) Input test data compression based on the reuse of parts of dictionary entries: static and dynamic approaches. IEEE Trans Comput Aided Des Integr Circuits Syst 32(11):1762–1775

Sathiyapriya R, Yuvasrri Sindhu M, Immanuel Rairosario P (2013) FPGA implementation of hybrid test data compression method using scan chain compaction and dictionary based scheme. Int J Sci Res Publ. ISSN 2250-3153

Author information

Authors and Affiliations

Corresponding author

Additional information

This article has been retracted. Please see the retraction notice for more detail: https://doi.org/10.1007/s10617-017-9196-6"

About this article

Cite this article

Sivanandam, L., Oorkavalan, U.M. & Periyasamy, S. RETRACTED ARTICLE: Test data compression for digital circuits using tetrad state skip scheme. Des Autom Embed Syst 21, 197–211 (2017). https://doi.org/10.1007/s10617-017-9196-6

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10617-017-9196-6