Abstract

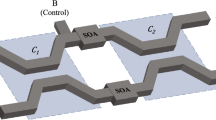

The choice of multiplier and accumulation unit determines the performance of digital signal processors, particularly in Big-Data correlators employed in radio interferometers. This work is targeted towards reducing the multiplier-size and delay in order to achieve low-power and compact-area for interferometer correlators such as in SKA and VLBI. For this purpose different fast and hardware efficient algorithms are compared and combined to achieve a new optimized ASIC multiplier design for performing correlation in radio interferometry. Further, the optimized new multiplier design is incorporated into our previous correlation processing cell designs of CMAC, CoSMAC and PE in Balu and Hasan: IEEE. Access. 5 25353–25364, 2017. The improvement in performance is verified using the GlobalFoundries 28 nm HPP standard cell library.

Similar content being viewed by others

References

Mattmann, C.A., Hart, A., Cinquini, L., Lazio, J., Khudikyan, S., Jones, D., et al.: Scalable data mining, archiving, and big data Management for the Next Generation Astronomical Telescopes," in Big Data Management, Technologies, and Applications, ed: IGI Global, pp. 196–221 (2014)

Jones, K.D.L., Thompson, D.R., D'Addario, L., Navarro, R., Mattmann, C., WalidMajid, J.L., UmaaRebbapragada, R.P.: Big data challenges for large radio arrays. Aerospace conference, IEEE. 1–6 (2012)

Bunton, J.D.: SKA correlators and beamformers. In: Acoustics, speech and signal processing (ICASSP), 2015 IEEE International Conference on, pp. 5650–5653 (2015)

Thompson, A.R., Moran, J.M., Swenson, G.W. Jr.: Interferometry and synthesis in radio astronomy: SpringerOpen, 3rd Edition, (2017)

Carlson, B.: An analysis of the effects of phase dithering in a lag-based fringe-stopping XF correlator," NRC-EVLA Memo# 002, May 2000. [Online]. Available: https://library.nrao.edu/public/memos/evla/EVLAM_11.pdf

D. W. Hawkins: Digital lag (XF) correlator theory, California institute of technology, Owens Valley Radio Observatory, Pasadena, CA, Jan. 2002

Bunton, J.: Multi-resolution fx correlator. ALMA memo. 447, (2003)

Bunton, J.D.: An improved FX correlator. ALMA Memo. 342, (2000)

Romney, J.: Introduction to the special-domain (FX) correlator, VLBA Correlator Memorandum, vol. 60, (1986)

Bunton, J.: A cross multiply accumulate unit for FX Correlators, Alma Memo2001

Bunton, J.D.: SKA correlator advances," in The Square Kilometre Array: An Engineering Perspective, ed: Springer, pp. 251–259 (2005)

Lapshev, S., Hasan, S.R.: On the architecture for the X part of a very large FX correlator using two-accumulator CMACs. Exp. Astron. 41, 259–270 (2016)

Rajan, R.T., Bentum, M., Gunst, A., Boonstra, A.-J.: Distributed correlators for interferometry in space. in IEEE Aerospace Conference. 1–9 (2013)

A. Bunton, G. Hampson, E. Kooistra, and A. Mika: SKA CSP low CBF-detailed design document," SKA-TEL-CSP-00000552016

Balu, V.R., Hasan, S.R.: Computationally minimized X-part for FX correlator in big-data interferometers. IEEE Access. 5, 25353–25364 (2017)

Carlson, B.: The giant systolic array (GSA): Straw-man proposal for a multi-mega baseline correlator for the SKA, SKA Memo 127, August (2010)

Baudry, A.: The ALMA correlators: technical details, performance and status of the Main Array correlator. ALMA Newsletter. 7, 18–31 (2011)

Carlson, B.: Requirements and functional specification: EVLA correlator Chip, NRC Canada, Hertzberg Inst. of Astroph., Dominion Radio Obs., RFS Document A25082N0000. Revision. 2,

Urry, W., Wright, M., Dexter, M., MacMahon, D.: The ATA correlator. ATA Memo Ser. 73, (2007)

Weste, N.H., Eshraghian, K.: Principles of CMOS VLSI Design: a systems perspective second edition," Addision-Wesley Publishing, California, l994, (1994)

Wang, Y., Jiang, Y., Sha, E.: On area-efficient low power array multipliers. In: Electronics, Circuits and Systems, 2001. ICECS 2001. The 8th IEEE International Conference on, pp. 1429–1432 (2001)

Townsend, W.J., Swartzlander, E.E., Abraham, J.A.: A comparison of Dadda and Wallace multiplier delays, in Advanced signal processing algorithms, architectures, and implementations XIII, pp. 552–561 (2003)

M. H. Riaz, S. A. Ahmed, Q. Javaid, and T. Kamal, "Low power 4× 4 bit multiplier design using dadda algorithm and optimized full adder," in Applied Sciences and Technology (IBCAST), 2018 15th International Bhurban Conference on, 2018, pp. 392–396

Wallace, C.S.: A suggestion for a fast multiplier, IEEE Transactions on electronic Computers, pp. 14–17, (1964)

Waters, R.S., Swartzlander, E.E.: A reduced complexity Wallace multiplier reduction. IEEE Trans. Comput. 59, 1134–1137 (2010)

Booth, A.D.: A signed binary multiplication technique. Q. J. Mech. Appl. Math. 4, 236–240 (1951)

Madrid, P.E., Millar, B., Swartzlander, E.E.: Modified Booth algorithm for high radix fixed-point multiplication. IEEE Transactions on Very Large Scale Integration (VLSI) Systems. 1, 164–167 (1993)

Ercegovac, M.D., Lang, T.: Digital Arithmetic. Elsevier (2004)

Ercegovac, M.D., Lang, T.: Fast multiplication without carry-propagate addition. IEEE Trans. Comput. 39, 1385–1390 (1990)

Kolagotla, R.K., Srinivas, H.R., Burns, G.F.: VLSI implementation of a 200-MHz 16/spl times/16 left-to-right carry-free multiplier in 0.35/spl mu/m CMOS technology for next-generation DSPs," in Custom Integrated Circuits Conference, 1997., Proc. IEEE 1997, pp. 469–472 (1997)

Behrooz, P.: Computer arithmetic: algorithms and hardware designs. Oxford University Press, vol. 19, pp. 512583–512585, (2000)

ARM Artisan 28 nm SC9MC Standard Cell Libraries: [Online]. Available: https://www.arm.com/products/physical-ip/logic-ip/standardcell-libraries.php

Author information

Authors and Affiliations

Corresponding author

Additional information

Publisher’s note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

About this article

Cite this article

Balu, V.R., Hasan, S.M.R. New optimized ASIC multiplier in 28 nm CMOS for processing the X-part of FX correlator in radio interferometry. Exp Astron 47, 325–343 (2019). https://doi.org/10.1007/s10686-019-09630-2

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10686-019-09630-2