Abstract

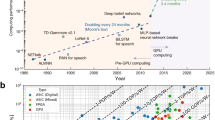

With the slowing down of the Moore’s law and fundamental limitations due to the von-Neumann bottleneck, continued improvements in computing hardware performance become increasingly more challenging. Resistive switching (RS) devices are being extensively studied as promising candidates for next generation memory and computing applications due to their fast switching speed, excellent endurance and retention, and scaling and three-dimensional (3D) stacking capability. In particular, RS devices offer the potential to natively emulate the functions and structures of synapses and neurons, allowing them to efficiently implement neural networks (NNs) and other in-memory computing systems for data intensive applications such as machine learning tasks. In this review, we will examine the mechanisms of RS effects and discuss recent progresses in the application of RS devices for memory, deep learning accelerator, and more faithful brain-inspired computing tasks. Challenges and possible solutions at the device, algorithm, and system levels will also be discussed.

Similar content being viewed by others

References

Moore, G. E. Cramming more components onto integrated circuits. Electronics1965, 38, 114–117.

Moore, G. E. Progress in digital integrated electronics. In Proceedings of the International Electron Devices Meeting, Washigton, DC, USA, 1975, pp 11–13.

Sutter, H. The free lunch is over: A fundamental turn toward concurrency in software. Dr. Dobb’s J.2005, 30, 202–210.

Taur, Y.; Buchanan, D. A.; Chen, W.; Frank, D. J.; Ismail, K. E.; Lo, S. H.; Sai-Halasz, G. A.; Viswanathan, R. G.; Wann, H. J. C.; Wind, S. J. et al. CMOS scaling into the nanometer regime. Proc. IEEE1997, 85, 486–504.

Frank, D. J.; Dennard, R. H.; Nowak, E.; Solomon, P. M.; Taur, Y.; Wong, H. S. P. Device scaling limits of Si MOSFETs and their application dependencies. Proc. IEEE2001, 89, 259–288.

Khan, H. N.; Hounshell, D. A.; Fuchs, E. R. H. Science and research policy at the end of Moore’S law. Nat. Electron.2018, 1, 14–21.

Wulf, W. A.; McKee, S. A. Hitting the memory wall: Implications of the obvious. ACM SIGARCH Comput. Arch. News1995, 23, 20–24.

Horowitz, M. Computing’s energy problem (and what we can do about it). In Proceedings of 2014 IEEE International Solid-State Circuits Conference Digest of Technical Papers, San Francisco, CA, USA, 2014, pp 10–14.

Zidan, M. A.; Strachan, J. P.; Lu, W. D. The future of electronics based on memristive systems. Nat. Electron.2018, 1, 22–29.

Yang, J. J.; Strukov, D. B.; Stewart, D. R. Memristive devices for computing. Nat. Nanotechnol.2013, 8, 13–24.

Xia, Q. F.; Yang, J. J. Memristive crossbar arrays for brain-inspired computing. Nat. Mater.2019, 18, 309–323.

Zhu, X. J.; Lee, S. H.; Lu, W. D. Nanoionic resistive-switching devices. Adv. Electron. Mater.2019, 5, 1900184.

Lee, J.; Lu, W. D. On-demand reconfiguration of nanomaterials: When electronics meets ionics. Adv. Mater.2018, 30, 1702770.

Waser, R.; Aono, M. Nanoionics-based resistive switching memories. Nat. Mater.2007, 6, 833–840.

Strukov, D. B.; Snider, G. S.; Stewart, D. R.; Williams, R. S. The missing memristor found. Nature2008, 453, 80–83.

Lam, C. H. Storage class memory. In Proceedings of 2010 10th IEEE International Conference on Solid-State and Integrated Circuit Technology, Shanghai, China, 2010, pp 1080–1083.

Burr, G. W.; Kurdi, B. N.; Scott, J. C.; Lam, C. H.; Gopalakrishnan, K.; Shenoy, R. S. Overview of candidate device technologies for storage-class memory. IBM J. Res. Dev.2008, 52, 449–464.

Sills, S.; Yasuda, S.; Strand, J.; Calderoni, A.; Aratani, K.; Johnson, A.; Ramaswamy, N. A copper ReRAM cell for storage class memory applications. In Proceedings of 2014 Symposium on VLSI Technology (VLSI-Technology): Digest of Technical Papers, Honolulu, HI, USA, 2014.

Ielmini, D.; Nardi, F.; Cagli, C. Universal reset characteristics of unipolar and bipolar metal-oxide RRAM. IEEE Trans. Electron Devices2011, 58, 3246–3253.

Choi, B. J.; Torrezan, A. C.; Strachan, J. P.; Kotula, P. G.; Lohn, A. J.; Marinella, M. J.; Li, Z. Y.; Williams, R. S.; Yang, J. J. High-speed and low-energy nitride memristors. Adv. Funct. Mater.2016, 26, 5290–5296.

Pi, S.; Li, C.; Jiang, H.; Xia, W. W.; Xin, H. L.; Yang, J.; Xia, Q. F. Memristor crossbar arrays with 6-nm half-pitch and 2-nm critical dimension. Nat. Nanotechnol.2019, 14, 35–39.

Govoreanu, B.; Kar, G. S.; Chen, Y. Y.; Paraschiv, V.; Kubicek, S.; Fantini, A.; Radu, I. P.; Goux, L.; Clima, S.; Degraeve, R. et al. 10 × 10 nm2 Hf/HfOx crossbar resistive RAM with excellent performance, reliability and low-energy operation. In Proceedings of 2011 International Electron Devices Meeting, Washington, DC, USA, 2011, pp 31.6.1–31.6.4.

Yang, J. J.; Zhang, M. X.; Strachan, J. P.; Miao, F.; Pickett, M. D.; Kelley, R. D.; Medeiros-Ribeiro, G.; Williams, R. S. High switching endurance in TaOx memristive devices. Appl. Phys. Lett.2010, 97, 232102.

Lee, M. J.; Lee, C. B.; Lee, D.; Lee, S. R.; Chang, M.; Hur, J. H.; Kim, Y. B.; Kim, C. J.; Seo, D. H.; Seo, S. et al. A fast, high-endurance and scalable non-volatile memory device made from asymmetric Ta2O5−x/TaO2−x bilayer structures. Nat. Mater.2011, 10, 625–630.

Handy, J. Understanding the intel/micron 3D XPoint memory. In Proceeding of 2015 Storage Developer Conference, Santa Clara 2015.

Ielmini, D.; Wong, H. S. P. In-memory computing with resistive switching devices. Nat. Electron.2018, 1, 333–343.

Di Ventra, M.; Pershin, Y. V. The parallel approach. Nat. Phys.2013, 9, 200–202.

Indiveri, G.; Liu, S. C. Memory and information processing in neuromorphic systems. Proc. IEEE2015, 103, 1379–1397.

Prezioso, M.; Merrikh-Bayat, F.; Hoskins, B. D.; Adam, G. C.; Likharev, K. K.; Strukov, D. B. Training and operation of an integrated neuromorphic network based on metal-oxide memristors. Nature2015, 521, 61–64.

Li, C.; Hu, M.; Li, Y. N.; Jiang, H.; Ge, N.; Montgomery, E.; Zhang, J. M.; Song, W. H.; Dávila, N.; Graves, C. E. et al. Analogue signal and image processing with large memristor crossbars. Nat. Electron.2018, 7, 52–59.

Hu, M.; Graves, C. E.; Li, C.; Li, Y. N.; Ge, N.; Montgomery, E.; Davila, N.; Jiang, H.; Williams, R. S.; Yang, J. J. et al. Memristor-based analog computation and neural network classification with a dot product engine. Adv. Mater.2018, 30, 1705914.

Jo, S. H.; Chang, T.; Ebong, I.; Bhadviya, B. B.; Mazumder, P.; Lu, W. Nanoscale memristor device as synapse in neuromorphic systems. Nano Lett.2010, 10, 1297–1301.

Wang, Z. R.; Joshi, S.; Savel’ev, S. E.; Jiang, H.; Midya, R.; Lin, P.; Hu, M.; Ge, N.; Strachan, J. P.; Li, Z. Y. et al. Memristors with diffusive dynamics as synaptic emulators for neuromorphic computing. Nat. Mater.2017, 16, 101–108.

Chua, L. O. Memristor-the missing circuit element. IEEE Trans. Circuit Theory1971, 78, 507–519.

Chua, L. O.; Kang, S. M. Memristive devices and systems. Proc. IEEE1976, 64, 209–223.

Waser, R.; Dittmann, R.; Staikov, C.; Szot, K. Redox-based resistive switching memories-nanoionic mechanisms, prospects, and challenges. Adv. Mater.2009, 27, 2632–2663.

Valov, I.; Lu, W. D. Nanoscale electrochemistry using dielectric thin films as solid electrolytes. Nanoscale2016, 8, 13828–13837.

Adam, G. C.; Hoskins, B. D.; Prezioso, M.; Strukov, D. B. Optimized stateful material implication logic for three-dimensional data manipulation. Nano Res.2016, 9, 3914–3923.

Russo, U.; Kamalanathan, D.; Ielmini, D.; Lacaita, A. L.; Kozicki, M. N. Study of multilevel programming in programmable metallization cell (PMC) memory. IEEE Trans. Electron Devices2009, 56, 1040–1047.

Menzel, S.; Böttger, U.; Waser, R. Simulation of multilevel switching in electrochemical metallization memory cells. J. Appl. Phys.2012, 111, 014501.

Balatti, S.; Larentis, S.; Gilmer, D. C.; Ielmini, D. Multiple memory states in resistive switching devices through controlled size and orientation of the conductive filament. Adv. Mater.2013, 25, 1474–1478.

Burr, G. W.; Shenoy, R. S.; Virwani, K.; Narayanan, P.; Padilla, A.; Kurdi, B.; Hwang, H. Access devices for 3D crosspoint memory. J. Vac. Sci. Technol. B2014, 32, 040802.

Kim, G. H.; Lee, J. H.; Ahn, Y.; Jeon, W.; Song, S. J.; Seok, J. Y.; Yoon, J. H.; Yoon, K. J.; Park, T. J.; Hwang, C. S. 32 × 32 crossbar array resistive memory composed of a stacked schottky diode and unipolar resistive memory. Adv. Funct. Mater.2013, 23, 1440–1449.

Choi, B. J.; Zhang, J. M.; Norris, K.; Gibson, G.; Kim, K. M.; Jackson, W.; Zhang, M. X. M.; Li, Z. Y.; Yang, J. J.; Williams, R. S. Trilayer tunnel selectors for memristor memory cells. Adv. Mater.2016, 28, 356–362.

Govoreanu, B.; Adelmann, C.; Redolfi, A.; Zhang, L. Q.; Clima, S.; Jurczak, M. High-performance metal-insulator-metal tunnel diode selectors. IEEE Electron Device Lett.2014, 35, 63–65.

Kau, D.; Tang, S.; Karpov, I. V.; Dodge, R.; Klehn, B.; Kalb, J. A.; Strand, J.; Diaz, A.; Leung, N.; Wu, J. et al. A stackable cross point phase change memory. In Proceedings of 2009 IEEE International Electron Devices Meeting, Baltimore, MD, USA, 2009, pp 1–4.

Zahurak, J.; Miyata, K.; Fischer, M.; Balakrishnan, M.; Chhajed, S.; Wells, D.; Li, H.; Torsi, A.; Lim, J.; Korber, M. et al. Process integration of a 27nm, 16Gb Cu ReRAM. In Proceedings of 2014 IEEE International Electron Devices Meeting, San Francisco, CA, USA, 2014, pp 6.2.1–6.2.4.

Baek, I. G.; Park, C. J.; Ju, H.; Seong, D. J.; Ahn, H. S.; Kim, J. H.; Yang, M. K.; Song, S. H.; Kim, E. M.; Park, S. O. et al. Realization of vertical resistive memory (VRRAM) using cost effective 3D process. In Proceedings of 2011 International Electron Devices Meeting, Washington, DC, USA, 2011, pp 31.8.1–31.8.4.

Hsu, C. W.; Wan, C. C.; Wang, I. T.; Chen, M. C.; Lo, C. L.; Lee, Y. J.; Jang, W. Y.; Lin, C. H.; Hou, T. H. 3D vertical TaOx/TiO2 RRAM with over 103 self-rectifying ratio and sub-MA operating current. In Proceedings of 2013 IEEE International Electron Devices Meeting, Washington, DC, USA, 2013, pp 10.4.1–10.4.4.

Bai, Y.; Wu, H. Q.; Wu, R. G.; Zhang, Y.; Deng, N.; Yu, Z. P.; Qian, H. Study of multi-level characteristics for 3D vertical resistive switching memory. Sci. Rep.2014, 4, 5780.

Liu, T. Y.; Yan, T. H.; Scheuerlein, R.; Chen, Y. C.; Lee, J. K.; Balakrishnan, G.; Yee, G.; Zhang, H.; Yap, A.; Ouyang, J. W. et al. A 130.7mm2 2-layer 32Gb ReRAM memory device in 24nm technology. In Proceedings of 2013 IEEE International Solid-State Circuits Conference Digest of Technical Papers, San Francisco, CA, USA, 2013, pp 210–211.

Cai, F. X.; Correll, J. M.; Lee, S. H.; Lim, Y.; Bothra, V.; Zhang, Z. Y.; Flynn, M. P.; Lu, W. D. A fully integrated reprogrammable memristor-CMOS system for efficient multiply-accumulate operations. Nat. Electron.2019, 2, 290–299.

Yang, J. J.; Pickett, M. D.; Li, X. M.; Ohlberg, D. A. A.; Stewart, D. R.; Williams, R. S. Memristive switching mechanism for metal/oxide/metal nanodevices. Nat. Nanotechnol.2008, 3, 429–433.

Park, G. S.; Kim, Y. B.; Park, S. Y.; Li, X. S.; Heo, S.; Lee, M. J.; Chang, M.; Kwon, J. H.; Kim, M.; Chung, U. I. et al. In situ observation of filamentary conducting channels in an asymmetric Ta2O5−x/TaO2−x bilayer structure. Nat. Commun.2013, 4, 2382.

Kim, S.; Choi, S.; Lu, W. Comprehensive physical model of dynamic resistive switching in an oxide memristor. ACS Nano2014, 8, 2369–2376.

Nardi, F.; Balatti, S.; Larentis, S.; Ielmini, D. Complementary switching in metal oxides: Toward diode-less crossbar RRAMs. In Proceedings of 2011 International Electron Devices Meeting, Washington, DC, USA, 2011, pp 31.1.1–31.1.4.

Larentis, S.; Nardi, F.; Balatti, S.; Gilmer, D. C.; Ielmini, D. Resistive switching by voltage-driven ion migration in bipolar RRAM—Part II: Modeling. IEEE Trans. Electron Devices2012, 59, 2468–2475.

Kim, S.; Kim, S. J.; Kim, K. M.; Lee, S. R.; Chang, M.; Cho, E.; Kim, Y. B.; Kim, C. J.; -In Chung, U.; Yoo, I. K. Physical electro-thermal model of resistive switching in Bi-layered resistance-change memory. Sci. Rep.2013, 3, 1680.

Kresse, G.; Hafner, J. Ab initio molecular-dynamics simulation of the liquid-metal-amorphous-semiconductor transition in germanium. Phys. Rev. B1994, 49, 14251–14269.

Lee, J.; Schell, W.; Zhu, X. J.; Kioupakis, E.; Lu, W. D. Charge transition of oxygen vacancies during resistive switching in oxide-based RRAM. ACS Appl. Mater. Interfaces2019, 77, 11579–11586.

Valov, I.; Waser, R.; Jameson, J. R.; Kozicki, M. N. Electrochemical metallization memories—fundamentals, applications, prospects. Nanotechnology2011, 22, 254003.

Yang, Y. C.; Gao, P.; Gaba, S.; Chang, T.; Pan, X. Q.; Lu, W. Observation of conducting filament growth in nanoscale resistive memories. Nat. Commun.2012, 3, 732.

Tian, X. Z.; Wang, L. F.; Wei, J. K.; Yang, S. Z.; Wang, W. L.; Xu, Z.; Bai, X. D. Filament growth dynamics in solid electrolyte-based resistive memories revealed by in situ TEM. Nano Res.2014, 7, 1065–1072.

Gaba, S.; Cai, F. X.; Zhou, J. T.; Lu, W. D. Ultralow sub-1-nA operating current resistive memory with intrinsic non-linear characteristics. IEEE Electron Device Lett.2014, 35, 1239–1241.

Belmonte, A.; Celano, U.; Chen, Z.; Radhaskrishnan, J.; Redolfi, A.; Clima, S.; Richard, O.; Bender, H.; Kar, G. S.; Vandervorst, W. et al. Voltage-controlled reverse filament growth boosts resistive switching memory. Nano Res.2018, 11, 4017–4025.

Jo, S. H.; Kim, K. H.; Lu, W. High-density crossbar arrays based on a Si memristive system. Nano Lett.2009, 9, 870–874.

Yang, Y. C.; Gao, P.; Li, L. Z.; Pan, X. Q.; Tappertzhofen, S.; Choi, S.; Waser, R.; Valov, I.; Lu, W. D. Electrochemical dynamics of nanoscale metallic inclusions in dielectrics. Nat. Commun.2014, 5, 4232.

Kim, K. H.; Gaba, S.; Wheeler, D.; Cruz-Albrecht, J. M.; Hussain, T.; Srinivasa, N.; Lu, W. A functional hybrid memristor crossbar-array/CMOS system for data storage and neuromorphic applications. Nano Lett.2012, 12, 389–395.

Kawahara, A.; Azuma, R.; Ikeda, Y.; Kawai, K.; Katoh, Y.; Tanabe, K.; Nakamura, T.; Sumimoto, Y.; Yamada, N.; Nakai, N. et al. An 8Mb multi-layered cross-point ReRAM macro with 443MB/s write throughput. In Proceedings of 2012 IEEE International Solid-State Circuits Conference, San Francisco, CA, USA, 2012, pp 432–434.

Lee, H. D.; Kim, S. G.; Cho, K.; Hwang, H.; Choi, H.; Lee, J.; Lee, S. H.; Lee, H. J.; Suh, J.; Chung, S. O. et al. Integration of 4F2 selector-less crossbar array 2Mb ReRAM based on transition metal oxides for high density memory applications. In Proceedings of 2012 Symposium on VLSI Technology, Honolulu, HI, USA, 2012, pp 151–152.

Hsieh, M. C.; Liao, Y. C.; Chin, Y. W.; Lien, C. H.; Chang, T. S.; Chih, Y. D.; Natarajan, S.; Tsai, M. J.; King, Y. C.; Lin, C. J. Ultra high density 3D via RRAM in pure 28nm CMOS process. In Proceedings of 2013 IEEE International Electron Devices Meeting, Washington, DC, USA, 2013, pp 10.3.1–10.3.4.

Fackenthal, R.; Kitagawa, M.; Otsuka, W.; Prall, K.; Mills, D.; Tsutsui, K.; Javanifard, J.; Tedrow, K.; Tsushima, T.; Shibahara, Y. et al. A 16Gb ReRAM with 200MB/s write and 1GB/s read in 27nm technology. In Proceedings of 2014 IEEE International Solid-State Circuits Conference Digest of Technical Papers, San Francisco, CA, USA, 2014, pp 338–339.

Yao, P.; Wu, H. Q.; Gao, B.; Eryilmaz, S. B.; Huang, X. Y.; Zhang, W. Q.; Zhang, Q. T.; Deng, N.; Shi, L. P.; Wong, H. S. P. et al. Face classification using electronic synapses. Nat. Commun.2017, 8, 15199.

Silver, D.; Huang, A.; Maddison, C. J.; Guez, A.; Sifre, L.; Van Den Driessche, G.; Schrittwieser, J.; Antonoglou, I.; Panneershelvam, V.; Lanctot, M. et al. Mastering the game of go with deep neural networks and tree search. Nature2016, 529, 484–489.

Markram, H. The human brain project. Sci. Am.2012, 306, 50–55.

Markram, H.; Lübke, J.; Frotscher, M.; Sakmann, B. Regulation of synaptic efficacy by coincidence of postsynaptic APs and EPSPs. Science1997, 275, 213–215.

Chen, Y. H.; Krishna, T.; Emer, J. S.; Sze, V. Eyeriss: An energy-efficient reconfigurable accelerator for deep convolutional neural networks. IEEE J. Solid-State Circuits2017, 52, 127–138.

Jouppi, N. P.; Young, C.; Patil, N.; Patterson, D.; Agrawal, G.; Bajwa, R.; Bates, S.; Bhatia, S.; Boden, N.; Borchers, A. et al. In-datacenter performance analysis of a tensor processing unit. In Proceedings of the 44th Annual International Symposium on Computer Architecture, Toronto, ON, Canada, 2017, pp 1–12.

Sheridan, P. M.; Cai, F. X.; Du, C.; Ma, W.; Zhang, Z. Y.; Lu, W. D. Sparse coding with memristor networks. Nat. Nanotechnol.2017, 12, 784–789.

Chen, B.; Cai, F. X.; Zhou, J. T.; Ma, W.; Sheridan, P.; Lu, W. D. Efficient in-memory computing architecture based on crossbar arrays. In Proceedings of 2015 IEEE International Electron Devices Meeting, Washington, DC, USA, 2015, pp 17.5.1–17.5.4.

Xia, Q. F.; Robinett, W.; Cumbie, M. W.; Banerjee, N.; Cardinali, T. J.; Yang, J. J.; Wu, W.; Li, X. M.; Tong, W. M.; Strukov, D. B. et al. Memristor-CMOS hybrid integrated circuits for reconfigurable logic. Nano Lett.2009, 9, 3640–3645.

Burr, G. W.; Shelby, R. M.; Sidler, S.; Di Nolfo, C.; Jang, J.; Boybat, I.; Shenoy, R. S.; Narayanan, P.; Virwani, K.; Giacometti, E. U. et al. Experimental demonstration and tolerancing of a large-scale neural network (165 000 Synapses) using phase-change memory as the synaptic weight element. IEEE Trans. Electron Devices2015, 62, 3498–3507.

Kawahara, A.; Azuma, R.; Ikeda, Y.; Kawai, K.; Katoh, Y.; Hayakawa, Y.; Tsuji, K.; Yoneda, S.; Himeno, A.; Shimakawa, K. et al. An 8 Mb multi-layered cross-point ReRAM macro with 443 MB/s write throughput. IEEE J. Solid-State Circuits2013, 48, 178–185.

Huang, J. J.; Tseng, Y. M.; Hsu, C. W.; Hou, T. H. Bipolar nonlinear Ni/TiO2/Ni selector for 1S1R crossbar array applications. IEEE Electron Device Lett.2011, 32, 1427–1429.

Shin, J.; Kim, I.; Biju, K. P.; Jo, M.; Park, J.; Lee, J.; Jung, S.; Lee, W.; Kim, S.; Park, S. et al. TiO2-based metal-insulator-metal selection device for bipolar resistive random access memory cross-point application. J. Appl. Phys.2011, 109, 033712.

Lee, W.; Park, J.; Shin, J.; Woo, J.; Kim, S.; Choi, G.; Jung, S.; Park, S.; Lee, D.; Cha, E. et al. Varistor-type bidirectional switch (JMAX>107A/cm2, selectivity∼104) for 3D bipolar resistive memory arrays. In Proceedings of 2012 Symposium on VLSI Technology, Honolulu, HI, USA, 2012, pp 37–38.

Woo, J.; Song, J.; Moon, K.; Lee, J. H.; Cha, E.; Prakash, A.; Lee, D.; Lee, S.; Park, J.; Koo, Y. et al. Electrical and reliability characteristics of a scaled (∼30nm) tunnel barrier selector (W/Ta2O5/TaOx/TiO2/TiN) with excellent performance (JMAX > 107A/cm2). In Proceedings of 2014 Symposium on VLSI Technology (VLSI-Technology): Digest of Technical Papers, Honolulu, HI, USA, 2014.

Ovshinsky, S. R. Reversible electrical switching phenomena in disordered structures. Phys. Rev. Lett.1968, 21, 1450–1453.

Lee, M. J.; Lee, D.; Cho, S. H.; Hur, J. H.; Lee, S. M.; Seo, D. H.; Kim, D. S.; Yang, M. S.; Lee, S.; Hwang, E. et al. A plasma-treated chalcogenide switch device for stackable scalable 3D nanoscale memory. Nat. Commun.2013, 4, 2629.

Son, M.; Lee, J.; Park, J.; Shin, J.; Choi, G.; Jung, S.; Lee, W.; Kim, S.; Park, S.; Hwang, H. Excellent selector characteristics of nanoscale VO2 for high-density bipolar ReRAM applications. IEEE Electron Device Lett.2011, 32, 1579–1581.

Kim, W. G.; Lee, H. M.; Kim, B. Y.; Jung, K. H.; Seong, T. G.; Kim, S.; Jung, H. C.; Kim, H. J.; Yoo, J. H.; Lee, H. D. et al. NbO2-based low power and cost effective 1S1R switching for high density cross point ReRAM application. In Proceedings of 2014 Symposium on VLSI Technology (VLSI-Technology): Digest of Technical Papers, Honolulu, HI, USA, 2014.

Jo, S. H.; Kumar, T.; Narayanan, S.; Lu, W. D.; Nazarian, H. 3D-stackable crossbar resistive memory based on field assisted superlinear threshold (FAST) selector. In Proceedings of 2014 IEEE International Electron Devices Meeting, San Francisco, CA, USA, 2015, pp 6.7.1–6.7.4.

Jo, S. H.; Kumar, T.; Narayanan, S.; Nazarian, H. Cross-point resistive RAM based on field-assisted superlinear threshold selector. IEEE Trans. Electron Devices2015, 62, 3477–3481.

Li, C.; Belkin, D.; Li, Y. N.; Yan, P.; Hu, M.; Ge, N.; Jiang, H.; Montgomery, E.; Lin, P.; Wang, Z. et al. Efficient and self-adaptive in-situ learning in multilayer memristor neural networks. Nat. Commun.2018, 9, 2385.

Shafiee, A.; Nag, A.; Muralimanohar, N.; Balasubramonian, R.; Strachan, J. P.; Hu, M.; Williams, R. S.; Srikumar, V. ISAAC: A convolutional neural network accelerator with in-situ analog arithmetic in crossbars. In Proceedings of 2016 ACM/IEEE 43rd Annual International Symposium on Computer Architecture, Seoul, South Korea, 2016, pp 14–26.

Gokmen, T.; Vlasov, Y. Acceleration of deep neural network training with resistive cross-point devices: Design considerations. Front. Neurosci.2016, 10, 333.

Agarwal, S.; Quach, T. T.; Parekh, O.; Hsia, A. H.; DeBenedictis, E. P.; James, C. D.; Marinella, M. J.; Aimone, J. B. Energy scaling advantages of resistive memory crossbar based computation and its application to sparse coding. Front. Neurosci.2016, 9, 484.

Wang, W.; Pedretti, G.; Milo, V.; Carboni, R.; Calderoni, A.; Ramaswamy, N.; Spinelli, A. S.; Ielmini, D. Learning of spatiotemporal patterns in a spiking neural network with resistive switching synapses. Sci. Adv.2018, 4, eaat4752.

Ohno, T.; Hasegawa, T.; Tsuruoka, T.; Terabe, K.; Gimzewski, J. K.; Aono, M. Short-term plasticity and long-term potentiation mimicked in single inorganic synapses. Nat. Mater.2011, 10, 591–595.

Wang, Z. Q.; Xu, H. Y.; Li, X. H.; Yu, H.; Liu, Y. C.; Zhu, X. J. Synaptic learning and memory functions achieved using oxygen ion migration/diffusion in an amorphous InGaZnO memristor. Adv. Funct. Mater.2012, 22, 2759–2765.

Kim, S.; Du, C.; Sheridan, P.; Ma, W.; Choi, S.; Lu, W. D. Experimental demonstration of a second-order memristor and its ability to biorealistically implement synaptic plasticity. Nano Lett.2015, 15, 2203–2211.

Zidan, M. A.; Jeong, Y. J.; Lu, W. D. Temporal learning using second-order memristors. IEEE Trans. Nanotechnol.2017, 16, 721–723.

Pickett, M. D.; Medeiros-Ribeiro, G.; Williams, R. S. A scalable neuristor built with Mott memristors. Nat. Mater.2013, 12, 114–117.

Stoliar, P.; Tranchant, J.; Corraze, B.; Janod, E.; Besland, M. P.; Tesler, F.; Rozenberg, M.; Cario, L. A leaky-integrate-and-fire neuron analog realized with a Mott insulator. Adv. Funct. Mater.2017, 27, 1604740.

Feng, S.; Zhou, H. Y.; Dong, H. B. Using deep neural network with small dataset to predict material defects. Mater. Des.2019, 162, 300–310.

Lukoševičius, M.; Jaeger, H. Reservoir computing approaches to recurrent neural network training. Comput. Sci. Rev.2009, 3, 127–149.

Torrejon, J.; Riou, M.; Araujo, F. A.; Tsunegi, S.; Khalsa, G.; Querlioz, D.; Bortolotti, P.; Cros, V.; Yakushiji, K.; Fukushima, A. et al. Neuromorphic computing with nanoscale spintronic oscillators. Nature2017, 547, 428–431.

Jaeger, H.; Haas, H. Harnessing nonlinearity: Predicting chaotic systems and saving energy in wireless communication. Science2004, 304, 78–80.

Jaeger, H.; Lukoševičius, M.; Popovici, D.; Siewert, U. Optimization and applications of echo state networks with leaky-integrator neurons. Neural Networks2007, 20, 335–352.

Verstraeten, D.; Schrauwen, B.; Stroobandt, D. Reservoir-based techniques for speech recognition. In Proceedings of 2006 IEEE International Joint Conference on Neural Network Proceedings, Vancouver, BC, Canada, 2006, pp 1050–1053.

Du, C.; Cai, F. X.; Zidan, M. A.; Ma, W.; Lee, S. H.; Lu, W. D. Reservoir computing using dynamic memristors for temporal information processing. Nat. Commun.2017, 8, 2204.

Appeltant, L.; Soriano, M. C.; Van Der Sande, G.; Danckaert, J.; Massar, S.; Dambre, J.; Schrauwen, B.; Mirasso, C. R.; Fischer, I. Information processing using a single dynamical node as complex system. Nat. Commun.2011, 2, 468.

Moon, J.; Ma, W.; Shin, J. H.; Cai, F. X.; Du, C.; Lee, S. H.; Lu, W. D. Temporal data classification and forecasting using a memristor-based reservoir computing system. Nat. Electron.2019, 2, 480–487.

Borghetti, J.; Snider, G. S.; Kuekes, P. J.; Yang, J. J.; Stewart, D. R.; Williams, R. S. ‘Memristive’ switches enable ‘stateful’ logic operations via material implication. Nature2010, 464, 873–876.

Linn, E.; Rosezin, R.; Tappertzhofen, S.; Böttger, U.; Waser, R. Beyond von neumann—logic operations in passive crossbar arrays alongside memory operations. Nanotechnology2012, 23, 305205.

Gao, L. G.; Alibart, F.; Strukov, D. B. Programmable CMOS/memristor threshold logic. IEEE Trans. Nanotechnol.2013, 72, 115–119.

James, A. P.; Francis, L. R. V. J.; Kumar, D. S. Resistive threshold logic. IEEE Trans. Very Large Scale Integr. Syst.2014, 22, 190–195.

Jeong, D. S.; Kim, K. M.; Kim, S.; Choi, B. J.; Hwang, C. S. Memristors for energy-efficient new computing paradigms. Adv. Electron. Mater.2016, 2, 1600090.

Balatti, S.; Ambrogio, S.; Ielmini, D. Normally-off logic based on resistive switches—Part I: Logic gates. IEEE Trans. Electron Devices2015, 62, 1831–1838.

Huang, P.; Kang, J. F.; Zhao, Y. D.; Chen, S. J.; Han, R. Z.; Zhou, Z.; Chen, Z.; Ma, W. J.; Li, M.; Liu, L. F. et al. Reconfigurable nonvolatile logic operations in resistance switching crossbar array for large-scale circuits. Adv. Mater.2016, 28, 9758–9764.

Strukov, D. B.; Likharev, K. K. CMOL FPGA: A reconfigurable architecture for hybrid digital circuits with two-terminal nanodevices. Nanotechnology2005, 16, 888–900.

Snider, G. S.; Williams, R. S. Nano/CMOS Architectures Using a Field-Programmable Nanowire Interconnect. Nanotechnology2007, 78, 035204.

Menzel, S.; Kaupmann, P.; Waser, R. Understanding filamentary growth in electrochemical metallization memory cells using kinetic monte carlo simulations. Nanoscale2015, 7, 12673–12681.

Qin, S. J.; Liu, Z.; Zhang, G.; Zhang, J. Y.; Sun, Y. P.; Wu, H. Q.; Qian, H.; Yu, Z. P. Atomistic study of dynamics for metallic filament growth in conductive-bridge random access memory. Phys. Chem. Chem. Phys.2015, 17, 8627–8632.

Liu, Q.; Long, S. B.; Lv, H. B.; Wang, W.; Niu, J. B.; Huo, Z. L.; Chen, J. N.; Liu, M. Controllable growth of nanoscale conductive filaments in solid-electrolyte-based ReRAM by using a metal nanocrystal covered bottom electrode. ACS Nano2010, 4, 6162–6168.

Lee, J.; Du, C.; Sun, K.; Kioupakis, E.; Lu, W. D. Tuning ionic transport in memristive devices by graphene with engineered nanopores. ACS Nano2016, 10, 3571–3579.

Choi, S.; Tan, S. H.; Li, Z. F.; Kim, Y.; Choi, C.; Chen, P. Y.; Yeon, H.; Yu, S. M.; Kim, J. SiGe epitaxial memory for neuromorphic computing with reproducible high performance based on engineered dislocations. Nat. Mater.2018, 17, 335–340.

Chen, P. Y.; Peng, X. C.; Yu, S. M. NeuroSim+: An integrated device-to-algorithm framework for benchmarking synaptic devices and array architectures. In Proceedings of 2017 IEEE International Electron Devices Meeting, San Francisco, CA, USA, 2017, pp 6.1.1–6.1.4.

Sun, X. Y.; Yu, S. M. Impact of non-ideal characteristics of resistive synaptic devices on implementing convolutional neural networks. IEEE J. Emerg. Sel. Top. Circuits Syst.2019, 9, 570–579.

Ambrogio, S.; Narayanan, P.; Tsai, H.; Shelby, R. M.; Boybat, I.; Di Nolfo, C.; Sidler, S.; Giordano, M.; Bodini, M.; Farinha, N. C. P. et al. Equivalent-accuracy accelerated neural-network training using analogue memory. Nature2018, 558, 60–67.

Le Gallo, M.; Sebastian, A.; Mathis, R.; Manica, M.; Giefers, H.; Tuma, T.; Bekas, C.; Curioni, A.; Eleftheriou, E. Mixed-precision in-memory computing. Nat. Electron.2018, 1, 246–253.

Boybat, I.; Le Gallo, M.; Nandakumar, S. R.; Moraitis, T.; Parnell, T.; Tuma, T.; Rajendran, B.; Leblebici, Y.; Sebastian, A.; Eleftheriou, E. Neuromorphic computing with multi-memristive synapses. Nat. Commun.2018, 9, 2514.

Zidan, M. A.; Jeong, Y. J.; Lee, J.; Chen, B.; Huang, S.; Kushner, M. J.; Lu, W. D. A general memristor-based partial differential equation solver. Nat. Electron.2018, 7, 411–420.

Gao, L. G.; Chen, P. Y.; Yu, S. M. Programming protocol optimization for analog weight tuning in resistive memories. IEEE Electron Device Lett.2015, 36, 1157–1159.

Zidan, M. A.; Jeong, Y.; Shin, J. H.; Du, C.; Zhang, Z. Y.; Lu, W. D. Field-Programmable Crossbar Array (FPCA) for reconfigurable computing. IEEE Trans. Multi-Scale Comput. Syst.2018, 4, 698–710.

Jacob, B.; Kligys, S.; Chen, B.; Zhu, M. L.; Tang, M.; Howard, A.; Adam, H.; Kalenichenko, D. Quantization and training of neural networks for efficient integer-arithmetic-only inference. In Proceedings of 2018 IEEE/CVF Conference on Computer Vision and Pattern Recognition, Salt Lake City, UT, USA, 2018, pp 2704–2713.

Hubara, I.; Courbariaux, M.; Soudry, D.; El-Yaniv, R.; Bengio, Y. Quantized neural networks: Training neural networks with low precision weights and activations. J. Mach. Learn. Res.2018, 18, 1–30.

Xu, X. W.; Ding, Y. K.; Hu, S. X.; Niemier, M.; Cong, J.; Hu, Y.; Shi, Y. Y. Scaling for edge inference of deep neural networks. Nat. Electron.2018, 1, 216–222.

Acknowledgements

The authors thank insightful discussions with Dr. M. A. Zidan and J. Moon. This work was supported by in part by the National Science Foundation through awards CCF-1900675 and DMR-1810119. W. D. L. would like to thank Charlie for his tremendous support during his stay as a postdoc in the Lieber group from 2003–2005, and for his advice that led to the conception of the initial concept of metal-ion based RS devices.

Author information

Authors and Affiliations

Corresponding author

Ethics declarations

The authors declare no competing financial interests.

Rights and permissions

About this article

Cite this article

Lee, S.H., Zhu, X. & Lu, W.D. Nanoscale resistive switching devices for memory and computing applications. Nano Res. 13, 1228–1243 (2020). https://doi.org/10.1007/s12274-020-2616-0

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s12274-020-2616-0