当前位置:

X-MOL 学术

›

Int. J. Circ. Theory Appl.

›

论文详情

Our official English website, www.x-mol.net, welcomes your feedback! (Note: you will need to create a separate account there.)

A low-error, memory-based fast binary antilogarithmic converter

International Journal of Circuit Theory and Applications ( IF 2.3 ) Pub Date : 2021-02-28 , DOI: 10.1002/cta.2981 L. Guna Sekhar Sai Harsha 1 , Bhaskara Rao Jammu 1 , Visweswara Rao Samoju 1 , Sreehari Veeramachaneni 2 , Noor Mohammad S 3

International Journal of Circuit Theory and Applications ( IF 2.3 ) Pub Date : 2021-02-28 , DOI: 10.1002/cta.2981 L. Guna Sekhar Sai Harsha 1 , Bhaskara Rao Jammu 1 , Visweswara Rao Samoju 1 , Sreehari Veeramachaneni 2 , Noor Mohammad S 3

Affiliation

|

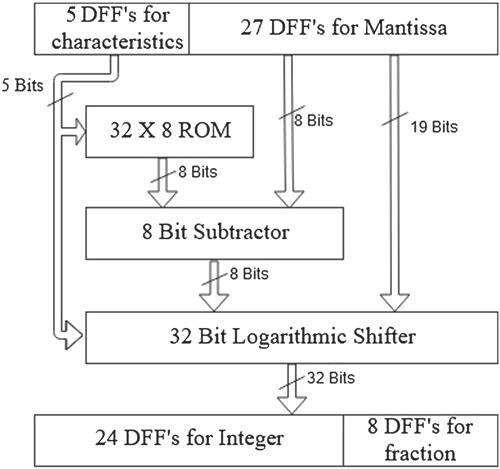

The ever-increasing need for high-performance signal processing blocks in avionics, machine learning (ML), IoT, neural networks, etc., has made the logarithmic arithmetic's as the front runner in advanced processors. The complex arithmetic operations such as multiplication and division can be easily performed in the logarithmic domain as they become addition and subtraction operations, respectively. However, the challenge is to perform the logarithmic and anti-logarithmic conversions and to optimize the trade-off between hardware complexity and accuracy. In this work, we propose a 32-bit antilogarithmic converter, for/using Mitchell's algorithm. The obtained results are corrected using the weighted average method. The correction terms are stored and selected using 32 × 8 ROM to decreases the computational speed and hardware complexity of the antilogarithmic converter. The proposed antilogarithmic converter has a maximum error percentage of 1.199%, which is 6.147% for Mitchell's algorithm while maintaining the hardware metrics close to Mitchell's algorithm.

中文翻译:

一种低误差、基于内存的快速二进制反对数转换器

航空电子、机器学习 (ML)、物联网、神经网络等领域对高性能信号处理模块的需求不断增长,使得对数算法成为高级处理器的领跑者。乘法和除法等复杂的算术运算可以在对数域中轻松执行,因为它们分别成为加法和减法运算。然而,挑战在于执行对数和反对数转换以及优化硬件复杂性和准确性之间的权衡。在这项工作中,我们提出了一个 32 位反对数转换器,用于/使用 Mitchell 算法。所得结果采用加权平均法进行修正。使用 32 × 8 ROM 存储和选择校正项,以降低反对数转换器的计算速度和硬件复杂性。所提出的反对数转换器的最大误差百分比为 1.199%,对于 Mitchell 算法来说是 6.147%,同时保持接近 Mitchell 算法的硬件指标。

更新日期:2021-02-28

中文翻译:

一种低误差、基于内存的快速二进制反对数转换器

航空电子、机器学习 (ML)、物联网、神经网络等领域对高性能信号处理模块的需求不断增长,使得对数算法成为高级处理器的领跑者。乘法和除法等复杂的算术运算可以在对数域中轻松执行,因为它们分别成为加法和减法运算。然而,挑战在于执行对数和反对数转换以及优化硬件复杂性和准确性之间的权衡。在这项工作中,我们提出了一个 32 位反对数转换器,用于/使用 Mitchell 算法。所得结果采用加权平均法进行修正。使用 32 × 8 ROM 存储和选择校正项,以降低反对数转换器的计算速度和硬件复杂性。所提出的反对数转换器的最大误差百分比为 1.199%,对于 Mitchell 算法来说是 6.147%,同时保持接近 Mitchell 算法的硬件指标。

京公网安备 11010802027423号

京公网安备 11010802027423号