Computers & Electrical Engineering ( IF 4.3 ) Pub Date : 2020-12-29 , DOI: 10.1016/j.compeleceng.2020.106947 Túlio Araujo , Matheus B.R. Cardoso , Erivelton G. Nepomuceno , Carlos H. Llanos , Janier Arias-Garcia

|

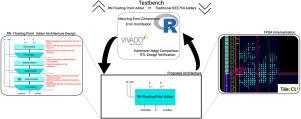

A well-known problem in the computer science area is related to numerical data representation, which directly affects adder circuits’ design and a reason to have different formats: IEEE Std. 754, Half-Unit-Biased (HUB), and Round-to-Nearest (RN). RN has an advantage that rounding to nearest is equivalent to a word truncation. It avoids double rounding errors and intermediate rounding steps with an exact conversion between formats, making it applicable to general problems. However, there is a lack of research on the hardware implementation of the RN representation. In this work, we propose hardware architectures for binary and floating-point adders, analyzing for the latter its performance in terms of error and resource consumption in FPGAs. To accomplish this, we have developed a one-bit RN-based adder that allows modular designs, considering an efficient signal propagation to obtain new architectures for both binary and floating-point single-precision adders. The results open new perspectives for further applications.

中文翻译:

一种新的基于浮点加法器的FPGA实现,使用数字的RN编码

在计算机科学领域,一个众所周知的问题与数值数据表示有关,它直接影响加法器电路的设计以及采用不同格式的原因:IEEE标准。754,半单位偏移(HUB)和最近舍入(RN)。RN的优势在于舍入到最接近等于单词截断。通过格式之间的精确转换,它避免了两次舍入错误和中间舍入步骤,使其适用于一般性问题。但是,对于RN表示的硬件实现尚缺乏研究。在这项工作中,我们提出了二进制和浮点加法器的硬件体系结构,并针对后者的性能在FPGA中的错误和资源消耗方面进行了分析。为此,我们开发了一种基于RN的1位加法器,该模块可进行模块化设计,考虑有效的信号传播以获得二进制和浮点单精度加法器的新架构。结果为进一步的应用开辟了新的前景。

京公网安备 11010802027423号

京公网安备 11010802027423号