当前位置:

X-MOL 学术

›

Int. J. Circ. Theory Appl.

›

论文详情

Our official English website, www.x-mol.net, welcomes your feedback! (Note: you will need to create a separate account there.)

Design and implementation of a hybrid DPWM under 50 ps resolution based on general‐purpose FPGA

International Journal of Circuit Theory and Applications ( IF 2.3 ) Pub Date : 2020-11-18 , DOI: 10.1002/cta.2898 Limin Yu 1 , Shen Xu 1 , Huaxin Zhang 1 , Longxing Shi 1 , Weifeng Sun 1

International Journal of Circuit Theory and Applications ( IF 2.3 ) Pub Date : 2020-11-18 , DOI: 10.1002/cta.2898 Limin Yu 1 , Shen Xu 1 , Huaxin Zhang 1 , Longxing Shi 1 , Weifeng Sun 1

Affiliation

|

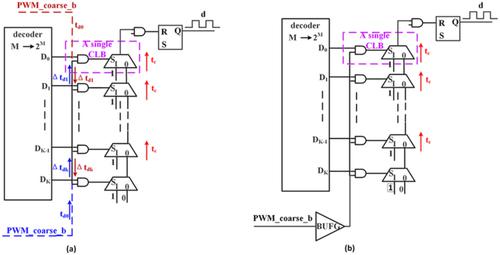

High‐resolution pulse width modulators are used widely in different fields of electrical engineering, such as dimming of light‐emitting diode (LED) lighting, motor control, RF modulators, audio amplifiers, and switch‐mode power supplies. To realize a high‐resolution digital pulse‐width modulator (DPWM) in a limited inner system clock, a simple implementation of a hybrid DPWM with the resolution under 50 ps based on a general‐purpose field‐programmable gate array (FPGA) is described. The multiplexer device implementing the fast carry‐chain path and an AND gate controlling the selection input are used as a delay unit. The manual routing or placement is not required in the proposed approach, which just needs some conditional constraints. Some different conditional constraints influencing the monotonicity and resolution of DPWM are discussed. Finally, a 1 MHz switching frequency DPWM with 40 ps resolution is experimentally demonstrated, with high monotonicity and linearity. Further, a synchronous buck with and without this high‐resolution DPWM is experimentally compared to illustrate the regulation resolution.

中文翻译:

基于通用FPGA的50 ps分辨率混合DPWM的设计与实现

高分辨率脉宽调制器广泛用于电气工程的不同领域,例如发光二极管(LED)照明的调光,电机控制,RF调制器,音频放大器和开关模式电源。为了在有限的内部系统时钟中实现高分辨率数字脉冲宽度调制器(DPWM),本文描述了一种基于通用现场可编程门阵列(FPGA)的,分辨率低于50 ps的混合DPWM的简单实现。 。实现快速进位链路径的多路复用器设备和控制选择输入的AND门用作延迟单元。提出的方法不需要手动布线或放置,只需要一些条件约束即可。讨论了影响DPWM单调性和分辨率的一些不同的条件约束。最后,实验证明了具有40 ps分辨率的1 MHz开关频率DPWM,具有高单调性和线性度。此外,通过实验比较了带有和不带有高分辨率DPWM的同步降压,以说明调节分辨率。

更新日期:2021-01-15

中文翻译:

基于通用FPGA的50 ps分辨率混合DPWM的设计与实现

高分辨率脉宽调制器广泛用于电气工程的不同领域,例如发光二极管(LED)照明的调光,电机控制,RF调制器,音频放大器和开关模式电源。为了在有限的内部系统时钟中实现高分辨率数字脉冲宽度调制器(DPWM),本文描述了一种基于通用现场可编程门阵列(FPGA)的,分辨率低于50 ps的混合DPWM的简单实现。 。实现快速进位链路径的多路复用器设备和控制选择输入的AND门用作延迟单元。提出的方法不需要手动布线或放置,只需要一些条件约束即可。讨论了影响DPWM单调性和分辨率的一些不同的条件约束。最后,实验证明了具有40 ps分辨率的1 MHz开关频率DPWM,具有高单调性和线性度。此外,通过实验比较了带有和不带有高分辨率DPWM的同步降压,以说明调节分辨率。

京公网安备 11010802027423号

京公网安备 11010802027423号