当前位置:

X-MOL 学术

›

Int. J. Circ. Theory Appl.

›

论文详情

Our official English website, www.x-mol.net, welcomes your feedback! (Note: you will need to create a separate account there.)

A reconfigurable real‐time neuromorphic hardware for spiking winner‐take‐all network

International Journal of Circuit Theory and Applications ( IF 2.3 ) Pub Date : 2020-10-01 , DOI: 10.1002/cta.2877 Behrooz Abdoli 1 , Saeed Safari 1

International Journal of Circuit Theory and Applications ( IF 2.3 ) Pub Date : 2020-10-01 , DOI: 10.1002/cta.2877 Behrooz Abdoli 1 , Saeed Safari 1

Affiliation

|

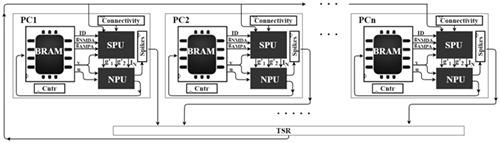

The central nervous system receives a vast amount of sensory inputs, and it should be able to discriminate and recognize different kinds of multisensory information. Winner‐take‐all (WTA) consists of a simple recurrent neural network carrying out discrimination of input signals through competition. This paper presents a real‐time scalable digital hardware implementation of the spiking WTA network. The need for concurrent computing, real‐time performance, proper accuracy, and the reconfigurable device has led to the field‐programmable gate array (FPGA) as the target hardware platform. A set of techniques is employed to lessen memory and resource usage. The proposed architecture consists of multiprocessing elements, which share hardware resources between a specific number of neurons. We introduce a novel connectivity array for neurons (dedicated to the WTA network) to cut down memory usage. Also, a multiplier‐less method in the neuron model and a novel tree adder in the synapse processing unit are designed to improve computational efficiency. The proposed network simulates 4,500 neurons in real time on a Xilinx Artix‐7 FPGA, while a scalable architecture facilitates the implementation of up to 20,000 neurons on this device. The pipeline structure can guarantee real‐time performance for large‐scale networks. Based on simulation and physical synthesis results, the presented network mimics biological WTA dynamics and consumes efficient hardware resources.

中文翻译:

可重配置的实时神经形态硬件,用于增强赢家通吃的网络

中枢神经系统接收大量的感觉输入,它应该能够区分和识别不同种类的多感觉信息。赢家通吃(WTA)包含一个简单的递归神经网络,该网络通过竞争对输入信号进行判别。本文介绍了尖峰WTA网络的实时可扩展数字硬件实现。对并行计算,实时性能,适当的精度以及可重新配置的设备的需求已导致现场可编程门阵列(FPGA)作为目标硬件平台。采用了一组技术来减少内存和资源的使用。所提出的体系结构由多处理元素组成,这些元素在特定数量的神经元之间共享硬件资源。我们为神经元(专用于WTA网络)引入了一种新颖的连通性阵列,以减少内存使用。此外,神经元模型中的无乘子方法和突触处理单元中的新型树加法器也被设计用来提高计算效率。拟议的网络在Xilinx Artix-7 FPGA上实时模拟4,500个神经元,而可扩展的架构则可在该设备上实现多达20,000个神经元的实现。流水线结构可以保证大型网络的实时性能。基于仿真和物理综合结果,该网络模仿了生物WTA动态,并消耗了有效的硬件资源。设计了神经元模型中的无乘法器方法和突触处理单元中的新型树加法器,以提高计算效率。拟议的网络在Xilinx Artix-7 FPGA上实时模拟4,500个神经元,而可扩展的架构则可在该设备上实现多达20,000个神经元的实现。流水线结构可以保证大型网络的实时性能。基于仿真和物理综合结果,该网络模仿了生物WTA动态,并消耗了有效的硬件资源。设计了神经元模型中的无乘法器方法和突触处理单元中的新型树加法器,以提高计算效率。拟议的网络在Xilinx Artix-7 FPGA上实时模拟4,500个神经元,而可扩展的架构则可在该设备上实现多达20,000个神经元的实现。流水线结构可以保证大型网络的实时性能。基于仿真和物理综合结果,该网络模仿了生物WTA动态,并消耗了有效的硬件资源。

更新日期:2020-12-04

中文翻译:

可重配置的实时神经形态硬件,用于增强赢家通吃的网络

中枢神经系统接收大量的感觉输入,它应该能够区分和识别不同种类的多感觉信息。赢家通吃(WTA)包含一个简单的递归神经网络,该网络通过竞争对输入信号进行判别。本文介绍了尖峰WTA网络的实时可扩展数字硬件实现。对并行计算,实时性能,适当的精度以及可重新配置的设备的需求已导致现场可编程门阵列(FPGA)作为目标硬件平台。采用了一组技术来减少内存和资源的使用。所提出的体系结构由多处理元素组成,这些元素在特定数量的神经元之间共享硬件资源。我们为神经元(专用于WTA网络)引入了一种新颖的连通性阵列,以减少内存使用。此外,神经元模型中的无乘子方法和突触处理单元中的新型树加法器也被设计用来提高计算效率。拟议的网络在Xilinx Artix-7 FPGA上实时模拟4,500个神经元,而可扩展的架构则可在该设备上实现多达20,000个神经元的实现。流水线结构可以保证大型网络的实时性能。基于仿真和物理综合结果,该网络模仿了生物WTA动态,并消耗了有效的硬件资源。设计了神经元模型中的无乘法器方法和突触处理单元中的新型树加法器,以提高计算效率。拟议的网络在Xilinx Artix-7 FPGA上实时模拟4,500个神经元,而可扩展的架构则可在该设备上实现多达20,000个神经元的实现。流水线结构可以保证大型网络的实时性能。基于仿真和物理综合结果,该网络模仿了生物WTA动态,并消耗了有效的硬件资源。设计了神经元模型中的无乘法器方法和突触处理单元中的新型树加法器,以提高计算效率。拟议的网络在Xilinx Artix-7 FPGA上实时模拟4,500个神经元,而可扩展的架构则可在该设备上实现多达20,000个神经元的实现。流水线结构可以保证大型网络的实时性能。基于仿真和物理综合结果,该网络模仿了生物WTA动态,并消耗了有效的硬件资源。

京公网安备 11010802027423号

京公网安备 11010802027423号