当前位置:

X-MOL 学术

›

Adv. Electron. Mater.

›

论文详情

Our official English website, www.x-mol.net, welcomes your feedback! (Note: you will need to create a separate account there.)

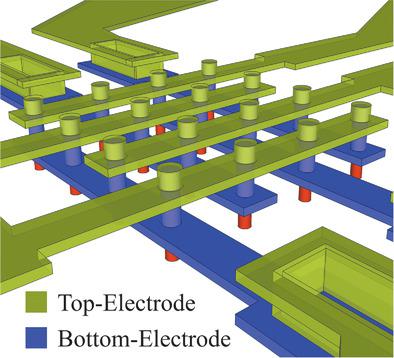

Cross‐Point Arrays with Low‐Power ITO‐HfO2 Resistive Memory Cells Integrated on Vertical III‐V Nanowires

Advanced Electronic Materials ( IF 6.2 ) Pub Date : 2020-05-11 , DOI: 10.1002/aelm.202000154 Karl‐Magnus Persson 1 , Mamidala Saketh Ram 1 , Olli‐Pekka Kilpi 1 , Mattias Borg 1, 2 , Lars‐Erik Wernersson 1

Advanced Electronic Materials ( IF 6.2 ) Pub Date : 2020-05-11 , DOI: 10.1002/aelm.202000154 Karl‐Magnus Persson 1 , Mamidala Saketh Ram 1 , Olli‐Pekka Kilpi 1 , Mattias Borg 1, 2 , Lars‐Erik Wernersson 1

Affiliation

|

Vertical nanowires with cointegrated metal‐oxide‐semiconductor field‐effect‐transistor (MOSFET) selectors and nonvolatile resistive random access memory (RRAM) cells represent a promising candidate for fast, energy‐efficient, cross‐point memory cells. This paper explores indium‐tin‐oxide‐hafnium‐dioxide RRAM cells integrated onto arrays of indium‐arsenide (InAs) vertical nanowires with a resulting area of 0.06 µm2 per cell. For low current operation, an improved switching uniformity over the intrinsic self‐compliant behavior is demonstrated when using an external InAs nanowire MOSFET selector in series. The memory cells show consistent switching voltages below ±1 V and a switching cycle endurance of 106 is demonstrated. The developed fabrication scheme is fully compatible with low‐ON‐resistance vertical III‐V nanowire MOSFET selectors, where operational compatibility with the initial high‐field filament forming is established. Due to the small footprint of a vertical implementation, high density integration is achievable, and with a measured programming energy for 50 ns pulses at 0.49 pJ, the technology promises fast and ultralow power cross‐point memory arrays.

中文翻译:

具有垂直III-V纳米线上集成的低功耗ITO-HfO2电阻存储单元的交叉点阵列

具有共集成的金属氧化物半导体场效应晶体管(MOSFET)选择器和非易失性电阻随机存取存储器(RRAM)单元的垂直纳米线是快速,节能,交叉点存储单元的有希望的候选者。本文探讨了集成到砷化铟(InAs)垂直纳米线阵列上的氧化铟锡二氧化ha RRAM单元,每个单元的最终面积为0.06 µm 2。对于低电流工作,当串联使用外部InAs纳米线MOSFET选择器时,可以证明在固有的自适应行为方面具有改善的开关均匀性。这些存储单元显示出低于±1 V的稳定开关电压,并且开关循环寿命为10 6被证明。所开发的制造方案与低导通电阻垂直III-V纳米线MOSFET选择器完全兼容,在这种选择器中,可以建立与初始高场长丝成型的操作兼容性。由于垂直实现的占用空间小,因此可以实现高密度集成,并且以0.49 pJ的50 ns脉冲测得的编程能量,该技术有望实现快速和超低功耗的交叉点存储阵列。

更新日期:2020-05-11

中文翻译:

具有垂直III-V纳米线上集成的低功耗ITO-HfO2电阻存储单元的交叉点阵列

具有共集成的金属氧化物半导体场效应晶体管(MOSFET)选择器和非易失性电阻随机存取存储器(RRAM)单元的垂直纳米线是快速,节能,交叉点存储单元的有希望的候选者。本文探讨了集成到砷化铟(InAs)垂直纳米线阵列上的氧化铟锡二氧化ha RRAM单元,每个单元的最终面积为0.06 µm 2。对于低电流工作,当串联使用外部InAs纳米线MOSFET选择器时,可以证明在固有的自适应行为方面具有改善的开关均匀性。这些存储单元显示出低于±1 V的稳定开关电压,并且开关循环寿命为10 6被证明。所开发的制造方案与低导通电阻垂直III-V纳米线MOSFET选择器完全兼容,在这种选择器中,可以建立与初始高场长丝成型的操作兼容性。由于垂直实现的占用空间小,因此可以实现高密度集成,并且以0.49 pJ的50 ns脉冲测得的编程能量,该技术有望实现快速和超低功耗的交叉点存储阵列。

京公网安备 11010802027423号

京公网安备 11010802027423号