当前位置:

X-MOL 学术

›

Int. J. Circ. Theory Appl.

›

论文详情

Our official English website, www.x-mol.net, welcomes your feedback! (Note: you will need to create a separate account there.)

Beyond algorithmic noise or how to shuffle parallel implementations?

International Journal of Circuit Theory and Applications ( IF 2.3 ) Pub Date : 2020-02-14 , DOI: 10.1002/cta.2756 Itamar Levi 1, 2 , Davide Bellizia 2 , François‐Xavier Standaert 2

International Journal of Circuit Theory and Applications ( IF 2.3 ) Pub Date : 2020-02-14 , DOI: 10.1002/cta.2756 Itamar Levi 1, 2 , Davide Bellizia 2 , François‐Xavier Standaert 2

Affiliation

|

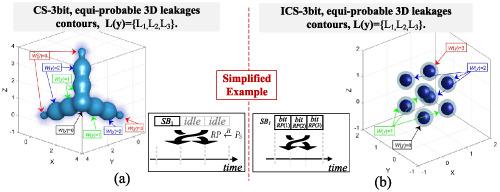

Noise is an important ingredient for side‐channel‐analysis countermeasures security. However, physical noise is in most cases not sufficient to achieve high‐security levels. As an outcome, designers traditionally aim to emulate noise by harnessing shuffling in the time domain and algorithmic noise in the amplitude domain. On one hand, harnessing algorithmic noise is limited in architectures/devices which have a limited data‐path width. On the other hand, the performance degradation due to shuffling is considerable. A natural complement to operation shuffling is the hardware‐based intra‐cycle shuffling (ICS), which typically shuffles the sample time of bits within a clock cycle (instead of micro‐processor operations). Such architecture eliminates the performance overhead due to shuffling within a single cycle, it is algorithm‐independent, i.e., no need in partitioning of operations, and as it is hardware‐based, the data‐path width can be tailored to better exploit algorithmic‐noise. In this manuscript, we first analyze the noise components in physical designs to better model the algorithmic noise. We then perform an information‐theoretic (IT) analysis of both shuffling countermeasures . The last part of the manuscript deals with real‐world architectures analysis: IT analysis of an Advanced Encryption Standard (AES) core implemented over a 32‐ and 128‐bit wide data‐path embedded with intra‐cycle shuffling and two flavors of shuffling generation (memory‐based and on‐line permutation generation). The manuscript is concluded by underling the benefits which can be achieved with the ICS architecture.

中文翻译:

超越算法噪声还是如何改组并行实现?

噪声是辅助信道分析对抗安全性的重要因素。但是,在大多数情况下,物理噪声不足以达到高安全级别。结果,设计人员传统上旨在通过利用时域混洗和幅度域算法噪声来模拟噪声。一方面,利用算法噪声的架构/设备具有有限的数据路径宽度。另一方面,由于改组而导致的性能下降是相当大的。基于硬件的周期内混洗(ICS)是对操作混洗的自然补充,它通常会在时钟周期内对位的采样时间进行混洗(而不是微处理器操作)。这种架构消除了由于在单个周期内进行混洗而导致的性能开销,它与算法无关,即 无需对操作进行分区,并且它是基于硬件的,因此可以调整数据路径的宽度以更好地利用算法噪声。在本手稿中,我们首先分析物理设计中的噪声成分,以更好地模拟算法噪声。然后,我们对这两种改组对策进行信息理论(IT)分析。该手稿的最后一部分涉及现实世界的体系结构分析:对高级加密标准(AES)内核的IT分析,该内核在32位和128位宽数据路径上实现,并嵌入了周期内混洗和两种混洗生成(基于内存和在线排列的生成)。通过强调ICS架构可以实现的好处来总结手稿。可以调整数据路径的宽度,以更好地利用算法噪声。在本手稿中,我们首先分析物理设计中的噪声成分,以更好地模拟算法噪声。然后,我们对这两种改组对策进行信息理论(IT)分析。该手稿的最后一部分涉及真实世界的体系结构分析:对高级加密标准(AES)内核的IT分析,该内核在32位和128位宽数据路径上实现,并嵌入了周期内混洗和两种混洗(基于内存和在线排列的生成)。通过强调ICS架构可以实现的好处来总结手稿。可以调整数据路径的宽度,以更好地利用算法噪声。在本手稿中,我们首先分析物理设计中的噪声成分,以更好地模拟算法噪声。然后,我们对两种改组对策进行信息理论(IT)分析。该手稿的最后一部分涉及真实世界的体系结构分析:对高级加密标准(AES)内核的IT分析,该内核在32位和128位宽数据路径上实现,并嵌入了周期内混洗和两种混洗(基于内存和在线排列的生成)。通过强调ICS架构可以实现的好处来总结手稿。然后,我们对这两种改组对策进行信息理论(IT)分析。该手稿的最后一部分涉及真实世界的体系结构分析:对高级加密标准(AES)内核的IT分析,该内核在32位和128位宽数据路径上实现,并嵌入了周期内混洗和两种混洗(基于内存和在线排列的生成)。通过强调ICS架构可以实现的好处来总结手稿。然后,我们对两种改组对策进行信息理论(IT)分析。该手稿的最后一部分涉及真实世界的体系结构分析:对高级加密标准(AES)内核的IT分析,该内核在32位和128位宽数据路径上实现,并嵌入了周期内混洗和两种混洗(基于内存和在线排列的生成)。通过强调ICS架构可以实现的好处来总结手稿。对在32位和128位宽数据路径上实现的高级加密标准(AES)内核的IT分析,该数据路径嵌入了周期内混洗和两种混洗生成方式(基于内存和在线置换生成)。通过强调ICS架构可以实现的好处来总结手稿。对在32位和128位宽数据路径上实现的高级加密标准(AES)内核的IT分析,该数据路径嵌入了周期内混洗和两种混洗生成方式(基于内存和在线置换生成)。通过强调ICS架构可以实现的好处来总结手稿。

更新日期:2020-02-14

中文翻译:

超越算法噪声还是如何改组并行实现?

噪声是辅助信道分析对抗安全性的重要因素。但是,在大多数情况下,物理噪声不足以达到高安全级别。结果,设计人员传统上旨在通过利用时域混洗和幅度域算法噪声来模拟噪声。一方面,利用算法噪声的架构/设备具有有限的数据路径宽度。另一方面,由于改组而导致的性能下降是相当大的。基于硬件的周期内混洗(ICS)是对操作混洗的自然补充,它通常会在时钟周期内对位的采样时间进行混洗(而不是微处理器操作)。这种架构消除了由于在单个周期内进行混洗而导致的性能开销,它与算法无关,即 无需对操作进行分区,并且它是基于硬件的,因此可以调整数据路径的宽度以更好地利用算法噪声。在本手稿中,我们首先分析物理设计中的噪声成分,以更好地模拟算法噪声。然后,我们对这两种改组对策进行信息理论(IT)分析。该手稿的最后一部分涉及现实世界的体系结构分析:对高级加密标准(AES)内核的IT分析,该内核在32位和128位宽数据路径上实现,并嵌入了周期内混洗和两种混洗生成(基于内存和在线排列的生成)。通过强调ICS架构可以实现的好处来总结手稿。可以调整数据路径的宽度,以更好地利用算法噪声。在本手稿中,我们首先分析物理设计中的噪声成分,以更好地模拟算法噪声。然后,我们对这两种改组对策进行信息理论(IT)分析。该手稿的最后一部分涉及真实世界的体系结构分析:对高级加密标准(AES)内核的IT分析,该内核在32位和128位宽数据路径上实现,并嵌入了周期内混洗和两种混洗(基于内存和在线排列的生成)。通过强调ICS架构可以实现的好处来总结手稿。可以调整数据路径的宽度,以更好地利用算法噪声。在本手稿中,我们首先分析物理设计中的噪声成分,以更好地模拟算法噪声。然后,我们对两种改组对策进行信息理论(IT)分析。该手稿的最后一部分涉及真实世界的体系结构分析:对高级加密标准(AES)内核的IT分析,该内核在32位和128位宽数据路径上实现,并嵌入了周期内混洗和两种混洗(基于内存和在线排列的生成)。通过强调ICS架构可以实现的好处来总结手稿。然后,我们对这两种改组对策进行信息理论(IT)分析。该手稿的最后一部分涉及真实世界的体系结构分析:对高级加密标准(AES)内核的IT分析,该内核在32位和128位宽数据路径上实现,并嵌入了周期内混洗和两种混洗(基于内存和在线排列的生成)。通过强调ICS架构可以实现的好处来总结手稿。然后,我们对两种改组对策进行信息理论(IT)分析。该手稿的最后一部分涉及真实世界的体系结构分析:对高级加密标准(AES)内核的IT分析,该内核在32位和128位宽数据路径上实现,并嵌入了周期内混洗和两种混洗(基于内存和在线排列的生成)。通过强调ICS架构可以实现的好处来总结手稿。对在32位和128位宽数据路径上实现的高级加密标准(AES)内核的IT分析,该数据路径嵌入了周期内混洗和两种混洗生成方式(基于内存和在线置换生成)。通过强调ICS架构可以实现的好处来总结手稿。对在32位和128位宽数据路径上实现的高级加密标准(AES)内核的IT分析,该数据路径嵌入了周期内混洗和两种混洗生成方式(基于内存和在线置换生成)。通过强调ICS架构可以实现的好处来总结手稿。

京公网安备 11010802027423号

京公网安备 11010802027423号