当前位置:

X-MOL 学术

›

Int. J. Circ. Theory Appl.

›

论文详情

Our official English website, www.x-mol.net, welcomes your feedback! (Note: you will need to create a separate account there.)

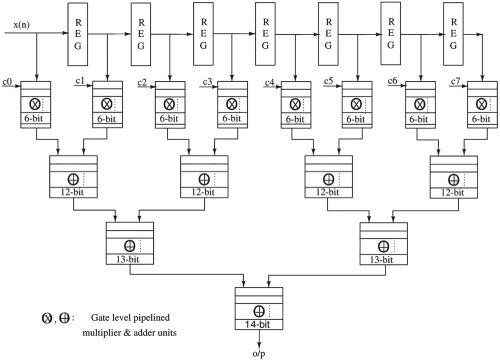

Design of high throughput asynchronous FIR filter using gate level pipelined multipliers and adders

International Journal of Circuit Theory and Applications ( IF 2.3 ) Pub Date : 2020-03-18 , DOI: 10.1002/cta.2771 K Sravani 1 , Rathnamala Rao 1

International Journal of Circuit Theory and Applications ( IF 2.3 ) Pub Date : 2020-03-18 , DOI: 10.1002/cta.2771 K Sravani 1 , Rathnamala Rao 1

Affiliation

|

This work presents the design of an asynchronous digital finite impulse response (FIR) filter suitable for high‐performance partial response maximum likelihood (PRML) read channel ICs. A high throughput, low latency FIR filter is the basic requirement for the equalization process in read channels. To achieve the enhancement in speed and reduction in latency of the FIR filter, its computational units are deeply pipelined using high‐capacity hybrid (HC‐hybrid) logic pipeline method. The designed FIR filter has been simulated using UMC‐180 nm and UMC‐65 nm technologies. Simulation results show that the asynchronous digital FIR filter can operate up to a throughput of 1.17 Giga items/s in 180 nm and 2.3 Giga items/s in 65 nm technology yet with the latency in the order of ns.

中文翻译:

利用门级流水线乘法器和加法器设计高吞吐量异步FIR滤波器

这项工作提出了适用于高性能部分响应最大似然(PRML)读取通道IC的异步数字有限脉冲响应(FIR)滤波器的设计。高吞吐量,低延迟的FIR滤波器是读取通道中均衡过程的基本要求。为了提高FIR滤波器的速度并减少其等待时间,使用高容量混合(HC-Hybrid)逻辑流水线方法对FIR滤波器的计算单元进行了深度流水线处理。设计的FIR滤波器已使用UMC-180 nm和UMC-65 nm技术进行了仿真。仿真结果表明,异步数字FIR滤波器在180 nm处的吞吐量可达1.17 Giga项/秒,在65 nm技术下的吞吐量高达2.3 Giga项/秒,而延迟却只有ns。

更新日期:2020-03-18

中文翻译:

利用门级流水线乘法器和加法器设计高吞吐量异步FIR滤波器

这项工作提出了适用于高性能部分响应最大似然(PRML)读取通道IC的异步数字有限脉冲响应(FIR)滤波器的设计。高吞吐量,低延迟的FIR滤波器是读取通道中均衡过程的基本要求。为了提高FIR滤波器的速度并减少其等待时间,使用高容量混合(HC-Hybrid)逻辑流水线方法对FIR滤波器的计算单元进行了深度流水线处理。设计的FIR滤波器已使用UMC-180 nm和UMC-65 nm技术进行了仿真。仿真结果表明,异步数字FIR滤波器在180 nm处的吞吐量可达1.17 Giga项/秒,在65 nm技术下的吞吐量高达2.3 Giga项/秒,而延迟却只有ns。

京公网安备 11010802027423号

京公网安备 11010802027423号