当前位置:

X-MOL 学术

›

Nanoscale Horiz.

›

论文详情

Our official English website, www.x-mol.net, welcomes your feedback! (Note: you will need to create a separate account there.)

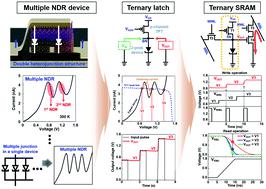

A multiple negative differential resistance heterojunction device and its circuit application to ternary static random access memory

Nanoscale Horizons ( IF 9.7 ) Pub Date : 2020-01-24 , DOI: 10.1039/c9nh00631a Kwan-Ho Kim 1, 2, 3, 4 , Hyung-Youl Park 1, 2, 3, 4 , Jaewoo Shim 5, 6, 7, 8 , Gicheol Shin 2, 3, 4, 9 , Maksim Andreev 1, 2, 3, 4 , Jiwan Koo 1, 2, 3, 4 , Gwangwe Yoo 1, 2, 3, 4 , Kilsu Jung 1, 2, 3, 4 , Keun Heo 1, 2, 3, 4 , Yoonmyung Lee 2, 3, 4, 9 , Hyun-Yong Yu 4, 10, 11, 12 , Kyung Rok Kim 4, 13, 14, 15 , Jeong Ho Cho 4, 16, 17, 18 , Sungjoo Lee 1, 2, 3, 4, 19 , Jin-Hong Park 1, 2, 3, 4, 19

Nanoscale Horizons ( IF 9.7 ) Pub Date : 2020-01-24 , DOI: 10.1039/c9nh00631a Kwan-Ho Kim 1, 2, 3, 4 , Hyung-Youl Park 1, 2, 3, 4 , Jaewoo Shim 5, 6, 7, 8 , Gicheol Shin 2, 3, 4, 9 , Maksim Andreev 1, 2, 3, 4 , Jiwan Koo 1, 2, 3, 4 , Gwangwe Yoo 1, 2, 3, 4 , Kilsu Jung 1, 2, 3, 4 , Keun Heo 1, 2, 3, 4 , Yoonmyung Lee 2, 3, 4, 9 , Hyun-Yong Yu 4, 10, 11, 12 , Kyung Rok Kim 4, 13, 14, 15 , Jeong Ho Cho 4, 16, 17, 18 , Sungjoo Lee 1, 2, 3, 4, 19 , Jin-Hong Park 1, 2, 3, 4, 19

Affiliation

|

For increasing the restricted bit-density in the conventional binary logic system, extensive research efforts have been directed toward implementing single devices with a two threshold voltage (VTH) characteristic via the single negative differential resistance (NDR) phenomenon. In particular, recent advances in forming van der Waals (vdW) heterostructures with two-dimensional crystals have opened up new possibilities for realizing such NDR-based tunneling devices. However, it has been challenging to exhibit three VTH through the multiple-NDR (m-NDR) phenomenon in a single device even by using vdW heterostructures. Here, we show the m-NDR device formed on a BP/(ReS2 + HfS2) type-III double-heterostructure. This m-NDR device is then integrated with a vdW transistor to demonstrate a ternary vdW latch circuit capable of storing three logic states. Finally, the ternary latch is extended toward ternary SRAM, and its high-speed write and read operations are theoretically verified.

中文翻译:

多重负差分电阻异质结器件及其电路在三态静态随机存取存储器中的应用

为了增加常规二进制逻辑系统中的受限位密度,已经针对通过单个负差分电阻(NDR)现象实现具有两个阈值电压(V TH)特性的单个器件进行了广泛的研究。特别地,利用二维晶体形成范德华(vdW)异质结构的最新进展为实现这种基于NDR的隧穿器件开辟了新的可能性。然而,即使通过使用vdW异质结构,在单个器件中通过多重NDR(m-NDR)现象表现出三个V TH仍然具有挑战性。在这里,我们显示了在BP /(ReS 2 + HfS 2)III型双异质结构。然后将此m-NDR器件与vdW晶体管集成在一起,以演示能够存储三个逻辑状态的三元vdW锁存电路。最后,将三元锁存器扩展到三元SRAM,并从理论上验证了其高速写入和读取操作。

更新日期:2020-01-24

中文翻译:

多重负差分电阻异质结器件及其电路在三态静态随机存取存储器中的应用

为了增加常规二进制逻辑系统中的受限位密度,已经针对通过单个负差分电阻(NDR)现象实现具有两个阈值电压(V TH)特性的单个器件进行了广泛的研究。特别地,利用二维晶体形成范德华(vdW)异质结构的最新进展为实现这种基于NDR的隧穿器件开辟了新的可能性。然而,即使通过使用vdW异质结构,在单个器件中通过多重NDR(m-NDR)现象表现出三个V TH仍然具有挑战性。在这里,我们显示了在BP /(ReS 2 + HfS 2)III型双异质结构。然后将此m-NDR器件与vdW晶体管集成在一起,以演示能够存储三个逻辑状态的三元vdW锁存电路。最后,将三元锁存器扩展到三元SRAM,并从理论上验证了其高速写入和读取操作。

京公网安备 11010802027423号

京公网安备 11010802027423号