Abstract

Recent advances in fabricating field-effect transistors with MoS2 and other related two-dimensional (2D) semiconductors have inspired the industry to begin with the integration of these emerging technologies into FAB-compatible process flows. Just like in the lab research on 2D devices performed in the last decade, focus during development is typically put on pure technology-related issues, such as low-temperature growth methods of large-area 2D films on target substrates, damage-free transfer from sacrificial substrates and growth of top-gate oxides. With maturing technology, the problem of stability limitations caused by oxide traps is gradually coming into focus now. Thus, here we report an in-depth analysis of hysteresis and bias-temperature instabilities for MoS2 FETs fabricated using a 300 mm FAB-compatible process. By performing a comprehensive statistical analysis on devices with top gate lengths ranging between 18 nm and 10 μm, we demonstrate that aggressive scaling results in additional stability problems, likely caused by defective edges of the scaled top gates, in particular at higher operation temperatures. These are important insights for understanding and addressing the stability limitations in future nanoscale 2D FETs produced using FAB process lines.

Similar content being viewed by others

Introduction

Molybdenum disulfide (MoS2)1,2,3,4 and other related two-dimensional (2D) semiconductors5,6,7 offer excellent opportunities to continue scaling modern electronic devices to keep up with Moore’s law8. Recently this topic has become increasingly important as the key performance parameters of prototype field-effect transistors (FETs), such as mobility, subthreshold swing and on/off current ratio, started to meet the requirements of modern integrated circuits9. These advances have been acknowledged by the semiconductor industry which is currently looking for suitable integration routes of 2D FET technologies into their FAB process flows10,11,12,13. For instance, Intel has recently developed a 300 mm FAB process for MoS2, WS2, WSe2 and MoSe2 at CMOS compatible temperatures12 and reported complementary integration of MoS2 n-type FETs and WSe2 p-type FETs11. TSMC has demonstrated nanoscale WS2 pFETs produced using channel area-selective chemical vapor deposition14. In addition, imec has also reported functional WS210 FETs fabricated using FAB-compatible process flows on 300 mm Si substrates. Considering these achievements, there is increasing hope that in the foreseeable future it should be possible to fabricate competitive CMOS-X circuits in which 2D materials will be used to enhance the scaling capabilities towards limits which cannot be reached solely with Si15.

In reality, the transition of 2D technologies from research labs to FAB process lines appears rather challenging13 since a large number of important questions need to be addressed. The most widely discussed of them is the need to match the CMOS thermal budget for back-end-of-line (BEOL) integration which must be below 450 °C12,13. This question is currently being addressed either by developing low-temperature growth methods of large-area 2D films, for instance by atomic-layer deposition (ALD)16, or by using metal-organic chemical-vapor deposition (MOCVD) with certain organometallic precursors12. Alternatively, high-temperature MOCVD can be used on sacrificial substrates with a subsequent transfer step that tries to minimize the damage10. Another important question is related to the fabrication of top-gated FETs which are required for circuit integration. When using presently available FAB lines this is only possible via ALD growth of conventional 3D oxides on top of 2D channels10,12. However, the oxides themselves and seed layers used for initial nucleation can contain a large amount of defects17. These defects can contribute to charge trapping and severely degrade the stable operation of 2D FETs by causing hysteresis18,19 and long-term drifts of the threshold voltage under gate bias stress20, known as bias-temperature instabilities (BTI)21,22. The question of the stability of 2D FETs with oxide insulators has not been fully addressed neither in previous lab research nor in the first studies on FAB devices, but could be a serious obstacle for further industry efforts.

To meet this demand, we report a comprehensive stability study of MoS2 FETs produced using the imec 300 mm FAB line. We analyze the dynamics of hysteresis and BTI in numerous devices with top gate lengths LTG ranging between 18 nm and 10 μm using temperatures up to 175 °C. Our statistical analysis suggests that the stability is limited due to the presence of many active oxide defects near the interface with the channel. Furthermore, when devices are scaled too much, additional degradation is observed. We trace this degradation back to the non-planar corners introduced at the edges of the top gate and suggest that it is attributed to the FAB process rather than the MoS2 channel which is used in our FETs. The effect of these corners starts to dominate below a certain gate length, in our case about 50 nm. These findings suggest that these corner effects must be avoided or at least minimized for future scaling attempts of 2D FETs in FAB lines.

Results and discussion

Fabrication and layout of our FAB MoS2 FETs

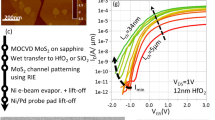

Our devices are top-gated MoS2 FETs fabricated using the imec FAB 300 mm process in the spirit of the previous work on WS2 devices with similar layout10. The schematic cross-section of these FETs is shown in Fig. 1a, and the fabrication process flow is provided in Fig. 1b. The MoS2 channel with 3.5 ML thickness was grown by MOCVD at 1000 °C on a 2 inch sapphire substrate and transferred onto a 300 mm device wafer (Fig. 1c) with a back gate oxide stack consisting of 50 nm thermal SiO2, 10 nm HfO2 grown by ALD and 5 nm SiO2 deposited by plasma-enhanced ALD (PEALD). The dry transfer method used10 is fully FAB-compatible and can serve as a good alternative to direct growth as it offers the possibility to perform MOCVD growth on sacrificial substrates at high temperatures, thereby enhancing the quality of MoS2 and matching BEOL requirements at once. Our MOCVD method is also fully compatible with 300 mm process10 and thus 2 inch MoS2 film was used only for simplicity. The top gate stack consisting of 10 nm HfO2 has been grown by ALD with 1.5 nm SiO2 seed layer deposited on top of MoS2 channel via molecular beam deposition (MBD). An additional 3 nm HfO2 underneath the top gate metal was deposited in the gate trench to avoid shorts to the channel material at the point where the gate extends out of the active area. The source/drain contacts in our devices were made of Ti/TiN/W and the top gate electrode of TiN/W. Finally, our FAB process flow includes etching of the VIA trench and Cu metallization. The device structure has been fully confirmed by transmission electron microscopy (TEM) measurements within the whole channel cross-section, including the areas underneath the top gate and source/drain contacts (Fig. 1d). We suspect that the oxide areas close to the edges of the top gate (marked in Fig. 1d) are of a poorer quality due to etching and thus contain a larger number of defects. As the total size of the left and right edges for large devices should be about 40-50 nm, for FETs with LTG below this value nearly all top gates should be formed by defective edges. This is also confirmed by the TEM images obtained for similar devices with LTG = 18 nm, see Supplementary Fig. 1.

a Schematic cross-section of the channel area of our MoS2 FETs. b Summary of imec FAB process flow used in this work. c Optical image of a 2 inch MoS2 film transferred onto a 300 mm device wafer with a back gate oxide stack. d TEM image of the channel area of our MoS2 FETs. Zoomed images show the areas underneath the top gate and drain electrodes. Defective corners are marked with red squares and are estimated to have a total size of 40–50 nm.

In order to perform a statistical analysis of the impact of scaling on the stability of our MoS2 FETs, we have fabricated several arrays containing 24 devices with LTG varied between 18 nm and 10 μm. According to TEM measurements, this results in a channel length LCH = LTG + 0.24μm. The channel width WCH is equal to 1 μm for all devices. In Fig. 2 we show the typical top gate transfer (ID–VTG) characteristics of the devices with LTG of 18 nm (Fig. 2a) and 0.43 μm (Fig. 2b) measured at different back gate voltages VBG. The corresponding output characteristics can be found in Supplementary Fig. 2. It is clear that for these first FAB MoS2 FETs SS is still far from near-deal values achieved for the best lab prototypes23 and tends to degrade for more scaled devices. In addition, SS can be modulated by applying VBG which also tunes the threshold voltage. At the same time, the on/off current ratio is already not far from 104 which is the minimum requirement for logic FETs.

Analysis of hysteresis in our FAB MoS2 FETs

We start with the statistical analysis of hysteresis in MoS2 FETs with different LTG at room temperature. In order to properly benchmark the dynamics of hysteresis caused by oxide defects with broadly distributed time constants, we measure double sweep gate transfer characteristics using different sweep rates and extract the dependences of hysteresis width ΔVH versus reciprocal sweep time 1/tsw. We extract hysteresis width using the constant current method as the difference between threshold voltages of the forward and reverse sweep curves, and thus ΔVH is positive if the hysteresis is clockwise and negative if it is counterclockwise. The typical double sweep ID–VTG characteristics measured for the devices with the smallest LTG = 18 nm and the largest LTG = 10 μm are shown in Fig. 3a, where we can see that for the nanoscale device the hysteresis is considerably smaller. In Fig. 3b we show the full set of ΔVH(1/tsw) traces measured for 8 devices with different LTG. The trend in ΔVH vs. 1/tsw dependences is similar for all devices and suggests some decrease in hysteresis for slower sweeps. However, for nanoscale FETs the hysteresis appears smaller already for fast sweeps and the slope of ΔVH(1/tsw) is much steeper which results in nearly zero hysteresis for slow sweeps. As will be shown below, this is because in nanoscale devices the contribution coming from defects situated near the top gate starts to compensate the standard clockwise hysteresis already at room temperature. In Fig. 3c we plot the dependences of ΔVH vs. LTG extracted for fast and slow sweep rates using the data measured for 16 devices. It can be clearly seen that a sizable decrease in the observed clockwise hysteresis starts for LTG of about 40–50 nm.

We note that for all our FETs the measured ΔVH(1/tsw) traces are not affected by the sequence of sweeps (i.e. first forward and then reverse or other way around, see Supplementary Fig. 3) and VBG applied during the measurements (Supplementary Fig. 4). However, VBG can modulate the device performance, and for most of our devices the use of VBG = 10 V results in Vth close to zero and an optimum drain current. On the other hand, for nanoscale FETs VBG = 5 V could be a good choice due to the typically more negative Vth (see Supplementary Fig. 4). Furthermore, the results of our hysteresis measurements are well reproducible after several months despite heating and intensive stressing of the devices (Supplementary Fig. 5).

Next, we attempt to understand the origin of the observed hysteresis dynamics and repeat our measurements at different temperatures. In Fig. 4a we show the ID–VTG characteristics measured using slow sweeps at 25 °C, 100 °C and 175 °C for a large FET with LTG = 10 μm. We observe a clockwise hysteresis which is barely dependent on temperature, as confirmed by ΔVH(1/tsw) traces provided in Fig. 4b (the corresponding ID–VTG characteristics measured using different sweep rates are shown in Supplementary Fig. 6). While a clockwise hysteresis is typically associated with charge trapping by border oxide traps24 situated within the first few nanometers from the channel/oxide interface25, a slight decay of the hysteresis width for slow sweeps can be explained by the fundamental shape of the ΔVH(1/tsw) dependence25. Since the number of defects in the oxide is finite and their time constants are broadly distributed26, this dependence commonly has a maximum at a certain 1/tsw which is shifted towards right at higher temperatures due to thermal activation of charge trapping. We have qualitatively reproduced this behavior by using our open-source framework Comphy27,28 which allows comprehensive simulation of reliability issues in 2D FETs by using a non-radiative (NMP) model22 to describe charge trapping (see more details in the Methods section and the model parameters in Supplementary Tables 1, 2). The obtained modeling results shown in Fig. 4c suggest that owing to a relatively broad defect band in the insulator, next to the maximum there is a plateau with a slight decay of ΔVH for slow sweeps. Thus, as marked in Fig. 4c our measurement range should fit this plateau, which would explain the weak temperature dependence of the measured ΔVH(1/tsw) traces with even some slight decrease of ΔVH for higher temperatures due to a shift of the maximum. Note that in our qualitative simulations we used a homogeneous spatial distribution of defects for simplicity. However, in reality, an inhomogeneous distribution with a larger density of defects near the oxide surface is more likely. This could explain why the slope of our simulated ΔVH(1/tsw) curves (Fig. 4c) within the measurement range is not as steep as for the experimental curves (Fig. 4b). The simulated gate transfer characteristics with the clockwise hysteresis and the corresponding band diagram are shown in Supplementary Fig. 8. We also note that it may be complicated to passivate border traps responsible for the clockwise hysteresis by using crystalline buffer layers such as hBN because the thickness required to fully block charge trapping would have to be about 2 nm. As this would make it difficult to achieve sub-1 nm equivalent oxide thickness which we are targeting in future, adding crystalline buffer layers would also complicate our FAB process.

a Double sweep ID–VTG characteristics of our MoS2 FETs with VTG of 10 μm measured at different temperatures. b The corresponding ΔVH vs. 1/tsw dependences. The hysteresis is always clockwise and barely dependent on temperature. c Qualitative ΔVH vs. 1/tsw dependences obtained from modeling with Comphy. The observed hysteresis dynamics can be explained by the impact of oxide defects situated near the interface with the channel.

In Fig. 5 we show the corresponding results for the nanoscale MoS2 FET with LTG = 18 nm. It can be seen that at 25 °C the hysteresis near Vth is small but still clockwise while at higher temperatures it becomes counterclockwise (Fig. 5a). The corresponding ΔVH(1/tsw) traces (Fig. 5b) confirm that at 100 °C and 175 °C the hysteresis direction turns from clockwise for fast sweeps to counterclockwise for slow sweeps (the related ID–VTG characteristics measured using different sweep rates are shown in Supplementary Fig. 7). Therefore, the small hysteresis initially observed for nanoscale FETs at 25 °C is actually an irrelevant improvement, as in reality another thermally activated mechanism of hysteresis comes into play together with scaling of the device geometry. In Fig. 5c we suggest an interpretation of the observed hysteresis dynamics based on the qualitative ΔVH(1/tsw) dependences obtained using our Comphy modeling setup (the gate transfer characteristics with the counterclockwise hysteresis and the corresponding band diagram are shown in Supplementary Fig. 9). It appears that in addition to faster defects situated near the channel/oxide interface, which are also present in large devices, in nanoscale FETs we are dealing with the contributions coming from relatively slow oxide traps situated near the top gate electrode. Therefore, the superposition of these two contributions is visible within our measurement range which explains the observed hysteresis dynamics with slight thermal activation of the counterclockwise hysteresis. Although the exact origin of these additional oxide defects near the top gate electrode is not completely clear, we think that they come from the corners of the nanoscale top gates which might become damaged during etching. As the gate length is increased, the relative contributions from these corners are reduced. Thus, since for larger FETs the relative contribution of the corners to the total LTG is negligible, we do not observe this counterclockwise hysteresis. This goes in line with the results shown in Fig. 3c, which confirm that the hysteresis starts to decrease for LTG below 40–50 nm, likely due to partial compensation of charge trapping at the MoS2/HfO2 interface by top gate edge defects.

a Double sweep ID–VTG characteristics of our MoS2 FETs with LTG = 18 nm measured at different temperatures. b The corresponding ΔVH vs. 1/tsw dependences. At higher temperatures the hysteresis becomes counterclockwise. c Qualitative ΔVH vs. 1/tsw dependences obtained from modeling with Comphy. The observed hysteresis dynamics can be explained by the impact of oxide defects situated near the interfaces with the top gate (counterclockwise) and the channel (clockwise).

Analysis of BTI in our FAB MoS2 FETs

Finally, we perform positive BTI (PBTI) measurements on the same devices using different stress voltages applied on the top gate using a constant stress time of ts = 10 ks. The results for our nanoscale MoS2 FET with LTG = 18 nm are shown in Fig. 6. Interestingly, for this long stress time PBTI degradation reverses towards the NBTI-like direction, an effect which becomes more pronounced for higher temperatures with even a slight NBTI-like recovery at 175 °C. This goes in line with the thermally activated counterclockwise hysteresis measured for the same device when using long sweep times (Fig. 5) and again suggests that oxide defects situated near the top gate electrode could be primarily responsible for the stability limitations of nanoscale FAB devices. As for large MoS2 FETs, we do not observe any reversal of PBTI (Supplementary Fig. 10) which is also consistent with the corresponding hysteresis results shown in Fig. 4.

In summary, we have performed the first comprehensive study of the reliability of 300 mm FAB MoS2 FETs and found that the dynamics of the commonly observed hysteresis and PBTI in these devices strongly depend on scaling. We demonstrate that while in micrometer-sized FETs these issues are due to charge trapping by oxide defects situated near the channel/oxide interface, nanoscale devices mostly suffer from thermally activated charge trapping near the top gate electrode which is dominated by defective corners. Based on these findings, we suggest that future attempts at producing nanoscale 2D FETs using FAB lines should pay more attention to possible process-induced defects near scaled top gates. Thus, our results are valuable for the future development of FAB processes of FETs with different 2D channels for modern integrated circuits.

Methods

Device fabrication

Our devices have been fabricated exclusively using the 300 mm FAB process line on degenerately doped Si substrates. First a 50 nm SiO2 was grown on the wafers to provide sufficient isolation for the deeper etched side contacts. Then a 10 nm HfO2 capped with a 5 nm PEALD SiO2 was grown on top to provide an etch stop for the top gate etch (HfO2) and an optimized surface for the MOCVD growth of MoS2. The transfer of the MoS2 was the only process steps performed in a clean lab environment, and the wafer was subsequently re-introduced into the FAB. Afterwards, the MBD-based SiO2 and 10 nm ALD HfO2 were deposited. The active patterning is performed with the initial high-k presence, to avoid oxidizing the sensitive MoS2 during the O2 ash used for resist stripping. Afterwards, the whole wafer was covered with a thick oxide in which the source/drain and gate trenches were etched. The source/drain electrodes were made of Ti/TiN/W and the top gate of TiN/W. Finally, the gate and contact trenches were contacted through a single damascene via and M1 routing made, using W and Cu for the via and M1 respectively.

Device characterization

The electrical characterization of our top-gated FETs was performed in the chamber of a Lakeshore vacuum probestation (10−6 Torr) using coupled Keithley 2602A and 2636B semiconductor parameter analyzers programmed in Python for uninterrupted measurements. In order to study the hysteresis, we have used our well-established measurement technique25 which uses repeating double sweeps of the gate transfer characteristics with different sweep times, ranging from hundreds of milliseconds to several hours. Subsequently, we extracted the hysteresis width ΔVH around the threshold voltage and plotted it versus the reciprocal sweep time 1/tsw. The PBTI measurements were done by measuring the ID–VTG characteristic of a fresh device, stressing by applying a certain VTG for a 10 ks stress time and subsequent monitoring of the recovery for several hours, while also repeating the measurements for 2–3 different VTG. This approach allows to extract PBTI drifts at different stress/recovery stages and to plot the obtained results versus the relaxation time, i.e. so-called BTI recovery traces22. All our measurements have been repeated at 25 °C, 100 °C and 175 °C.

Modeling

To simulate the hysteresis in our devices, we used our compact physics framework Comphy27,28. As a first step, we built the gate stack of the device using the parameters provided in Supplementary Table 1. In order to account for the non-idealities of the device, we added charge traps near the channel and gate side. The charge trapping was described by an effective two-state NMP model22, with each trap characterized by its position xt, trap level Et, relaxation energy Er, and curvature ratio R. The parameters of the charged traps used in our modeling setups are summarized in Supplementary Table 2. The traps were sampled with a Gaussian distribution for Et and Er and a uniform distribution for the depth xt. Our modeling results suggest that the traps placed close to the channel contribute to clockwise hysteresis and the traps placed close to the gate contribute to counterclockwise hysteresis.

Data availability

The data that support the findings of this work are available from the corresponding authors upon reasonable request.

References

Radisavljevic, B., Radenovic, A., Berivio, J., Giacometti, V. & Kis, A. Single-layer MoS2 transistors. Nat. Nanotechnol. 6, 147–150 (2011).

Bolshakov, P. et al. Improvement in top-gate MoS2 transistor performance due to high quality backside Al2O3 layer. Appl. Phys. Lett. 111, 032110 (2017).

Smithe, K., Suryavanshi, S., Munoz-Rojo, M., Tedjarati, A. & Pop, E. Low variability in synthetic monolayer MoS2 devices. ACS Nano 11, 8456–8463 (2017).

Si, M. et al. Steep-slope hysteresis-free negative capacitance MoS2 transistors. Nat. Nanotechnol. 13, 24–28 (2018).

Lin, Y.-F. et al. Ambipolar MoTe2 transistors and their applications in logic circuits. Adv. Mater. 26, 3263–3269 (2014).

Kumar, J., Kuroda, M. A., Bellus, M. Z., Han, S.-J. & Chiu, H.-Y. Full-range electrical characteristics of WS2 transistors. Appl. Phys. Lett. 106, 123508 (2015).

Chang, Y.-M. et al. reversible and precisely controllable p/n-type doping of MoTe2 transistors through electrothermal doping. Adv. Mater. 30, e1706995 (2018).

Schwierz, F., Pezoldt, J. & Granzner, R. Two-dimensional materials and their prospects in transistor electronics. Nanoscale 7, 8261–8283 (2015).

Das, S. et al. Transistors based on two-dimensional materials for future integrated circuits. Nat. Electron. 4, 786–799 (2021).

Asselberghs, I. et al. Wafer-scale integration of double gated WS2 transistors in 300mm Si CMOS Fab. In: 2020 IEEE International Electron Devices Meeting Technical Digest, 40.2.1–40.2.4 (2020).

Dorow, C. et al. Advancing Monolayer 2-D nMOS and pMOS transistor integration from growth to van der Waals interface engineering for ultimate CMOS scaling. IEEE Trans. Electron Devices 68, 6592–6598 (2021).

O’Brien, K. P. et al. Advancing 2D monolayer CMOS through contact, channel and interface engineering. In: 2020 IEEE International Electron Devices Meeting 7-1 (IEEE, 2021).

Schram, T., Sutar, S., Radu, I. & Asselberghs, I. Challenges of wafer-scale integration of 2d semiconductors for high-performance transistor circuits. Adv. Mater. 34, 2109796 (2022).

Cheng, C.-C. et al. First demonstration of 40-nm channel length top-gate WS2 pFET using channel area-selective CVD growth directly on SiOx/Si substrate. In: 2019 IEEE Symposium on VLSI Technological Circuits T244-T245 (IEEE, 2019).

Lemme, M. C., Akinwande, D., Huyghebaert, C. & Stampfer, C. 2D materials for future heterogeneous electronics. Nat. Commun. 13, 1392 (2022).

Deijkers, J. et al. MoS2 synthesized by atomic layer deposition as CU diffusion barrier. Adv. Mater. Interfaces 10, 2202426 (2023).

Illarionov, Y. et al. Insulators for 2D nanoelectronics: the gap to bridge. Nat. Commun. 11, 3385 (2020).

Guo, Y. et al. Charge trapping at the MoS2-SiO2 interface and its effects on the characteristics of MoS2 metal-oxide-semiconductor field effect transistors. Appl. Phys. Lett. 106, 103109 (2015).

Di Bartolomeo, A. et al. Hysteresis in the transfer characteristics of MoS2 transistors. 2D Mater. 5, 015014 (2017).

Illarionov, Y. et al. Improved hysteresis and reliability of MoS2 transistors with high-quality CVD growth and Al2O3 encapsulation. IEEE Electron Device Lett. 38, 1763–1766 (2017).

Huard, V. Two independent components modeling for negative bias temperature instability. In: 2010 IEEE International Reliability Physics Symposium 33–42 (2010).

Grasser, T. Stochastic charge trapping in oxides: from random telegraph noise to bias temperature instabilities. Microelectron. Reliab. 52, 39–70 (2012).

Vu, Q. et al. Near-zero hysteresis and near-ideal subthreshold swing in h-BN encapsulated single-layer MoS2 field-effect transistors. 2D Mater. 5, 031001 (2018).

Fleetwood, D. "Border traps” in MOS devices. IEEE Trans. Nucl. Sci. 39, 269–271 (1992).

Illarionov, Y. et al. The role of charge trapping in MoS2/SiO2 and MoS2/hBN field-effect transistors. 2D Mater. 3, 035004 (2016).

Grasser, T. et al. Analytic modeling of the bias temperature instability using capture/emission time maps. In: 2011 IEEE International Electron Devices Meeting Technical Digest, 27.4.1–27.4.4 (2011).

Rzepa, G. et al. Comphy—a compact-physics framework for unified modeling of BTI. Microelectron. Reliab. 85, 49–65 (2018).

Waldhoer, D. et al. Comphy v3.0—a compact-physics framework for modeling charge trapping related reliability phenomena in MOS devices. Microelectron. Reliab. 146, 115004 (2023).

Acknowledgements

This research was funded in part by the Austrian Science Fund (FWF) [I2606-N30, I4123-N30 (joint project with DFG LE 2440/7-1) and I5296-N] and also by the European Union’s Horizon 2020 research and innovation programme under grant agreement 952792 (2D-EPL). For open access purposes, the author has applied a CC BY public copyright license to any author accepted manuscript version arising from this submission. Furthermore, T.K. acknowledges financial support through the FFG under project no. 1755510. Y.Y.I. also acknowledges financial support by Shenzhen Science and Technology Program (20231115150611001) and the start up fund provided by SUSTech.

Author information

Authors and Affiliations

Contributions

Y.Y.I. performed the measurements of hysteresis and BTI and wrote the manuscript. A.K. and T.K. performed the modeling. Q.S., B.K., L.P., T.S., S.B., D.C. and I.A. contributed to the development of imec 300 mm FAB process. T.G. supervised the research. All authors discussed the results and contributed to the preparation of the manuscript.

Corresponding authors

Ethics declarations

Competing interests

The authors declare no competing interests.

Additional information

Publisher’s note Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Supplementary information

Rights and permissions

Open Access This article is licensed under a Creative Commons Attribution 4.0 International License, which permits use, sharing, adaptation, distribution and reproduction in any medium or format, as long as you give appropriate credit to the original author(s) and the source, provide a link to the Creative Commons license, and indicate if changes were made. The images or other third party material in this article are included in the article’s Creative Commons license, unless indicated otherwise in a credit line to the material. If material is not included in the article’s Creative Commons license and your intended use is not permitted by statutory regulation or exceeds the permitted use, you will need to obtain permission directly from the copyright holder. To view a copy of this license, visit http://creativecommons.org/licenses/by/4.0/.

About this article

Cite this article

Illarionov, Y.Y., Karl, A., Smets, Q. et al. Process implications on the stability and reliability of 300 mm FAB MoS2 field-effect transistors. npj 2D Mater Appl 8, 8 (2024). https://doi.org/10.1038/s41699-024-00445-0

Received:

Accepted:

Published:

DOI: https://doi.org/10.1038/s41699-024-00445-0